약 5분 소요

개요

목표

AXI4-Lite 인터페이스 기반 GPIO IP를 설계하고, Vitis에서 SW 프로그래밍으로 동작 검증하는 것을 목표로 한다.

환경

- Target HW

- Board: Basys3

- Processor: MicroBlaze

- Development Tools

- Vivado 2020.2

- Vitis 2020.2

IP 만들기

IP Packaging용 Vivado Project 생성

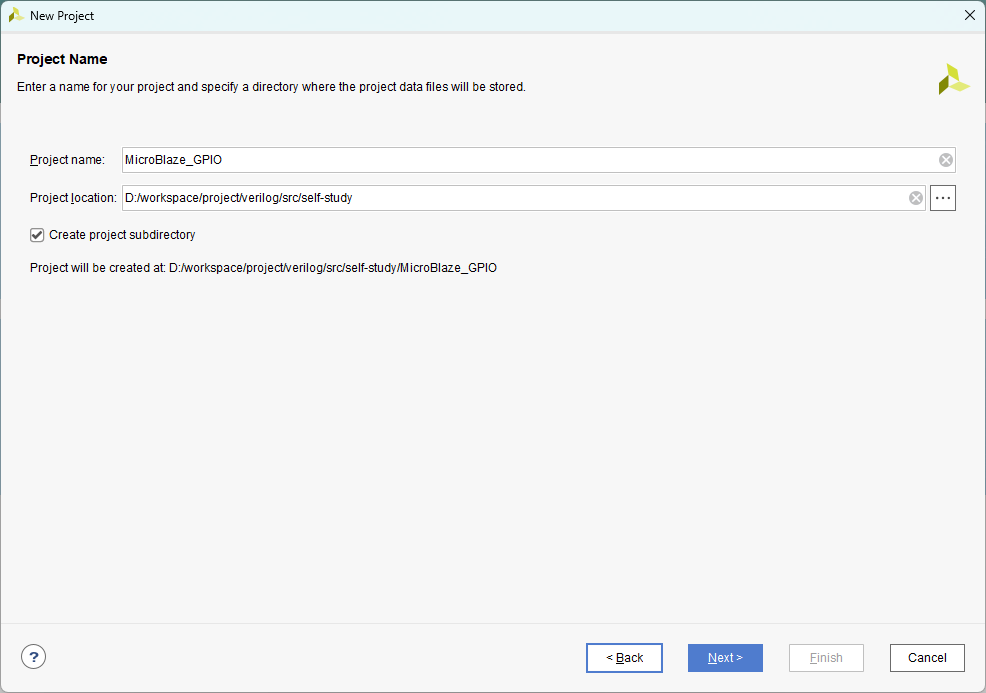

프로젝트 이름을 위와 같이 설정

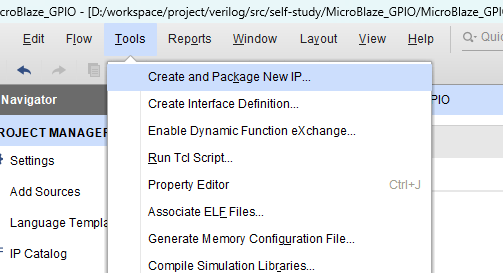

Vivado 창이 뜨면 Create and Package New IP … 클릭

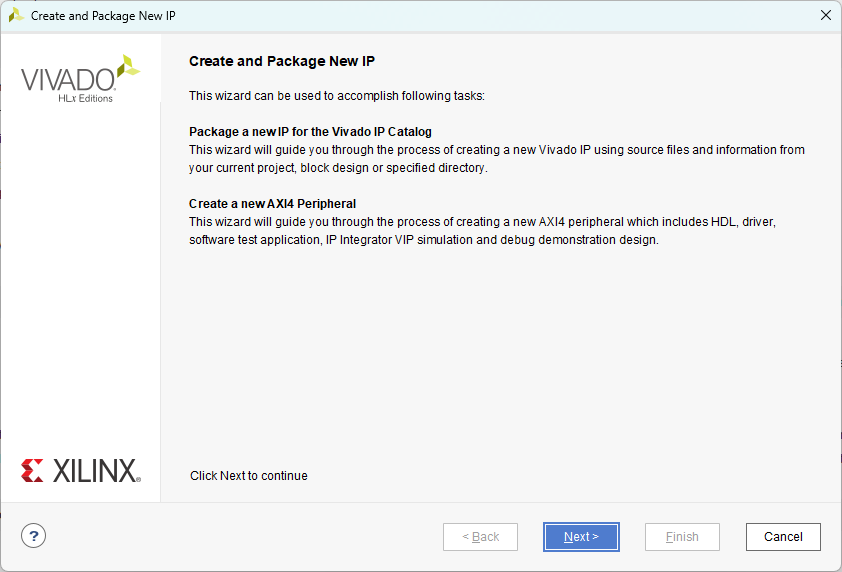

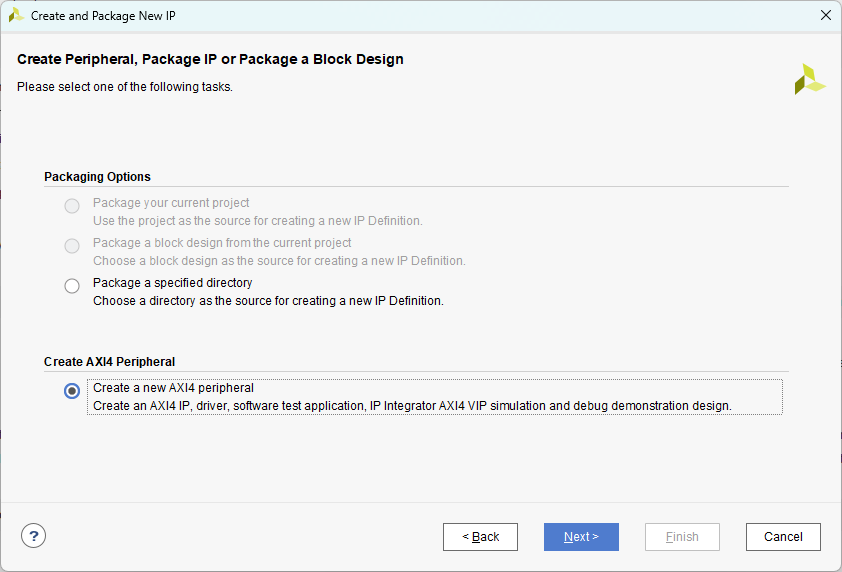

Create AXI4 Peripheral 선택 후 Next

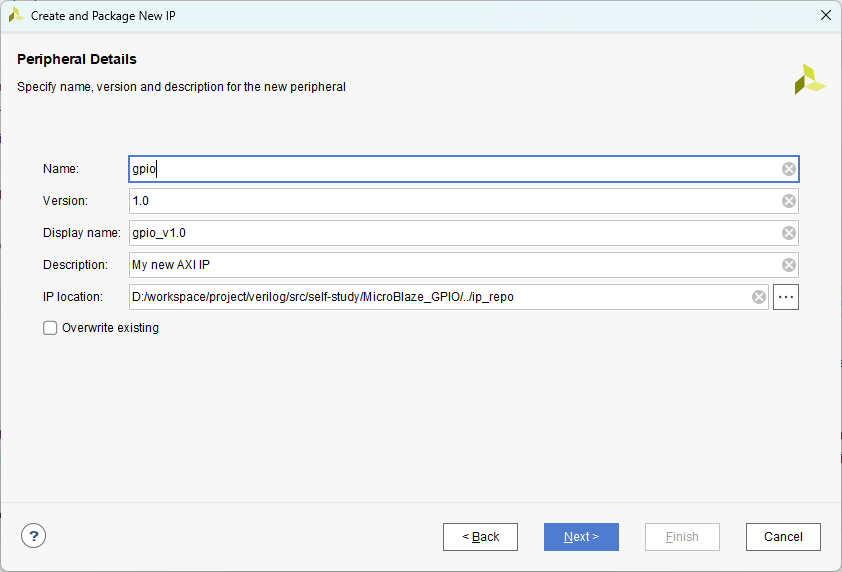

이름을 gpio로 변경 후 IP location 위치 확인 후 Next

IP location은 현재 프로젝트 폴더의 상위 폴더의 ip_repo로 설정되어있음

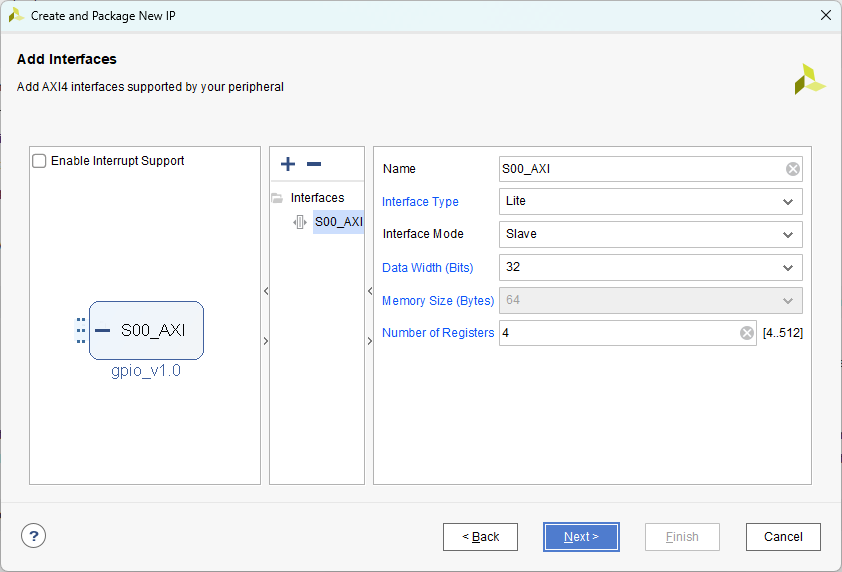

디폴트로 Next

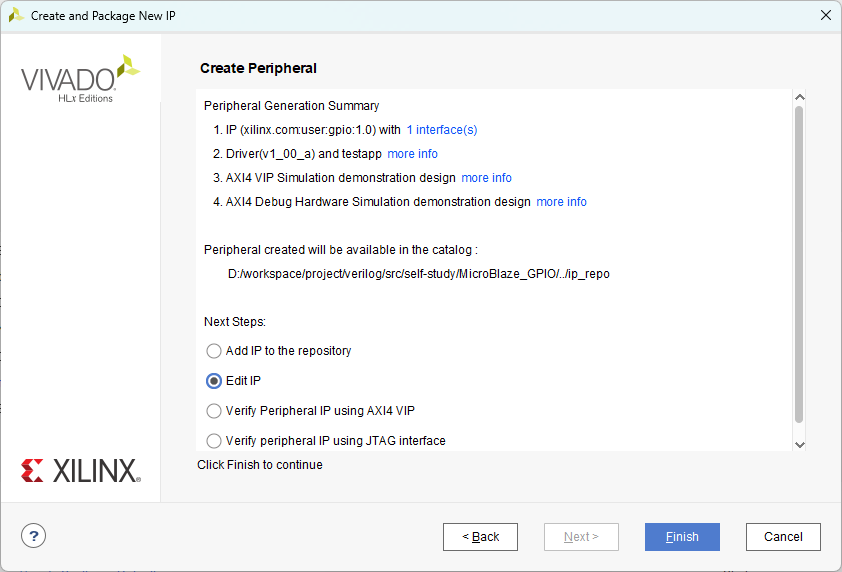

IP를 수정하여 사용할 것이므로 Edit IP 클릭 후 Finish

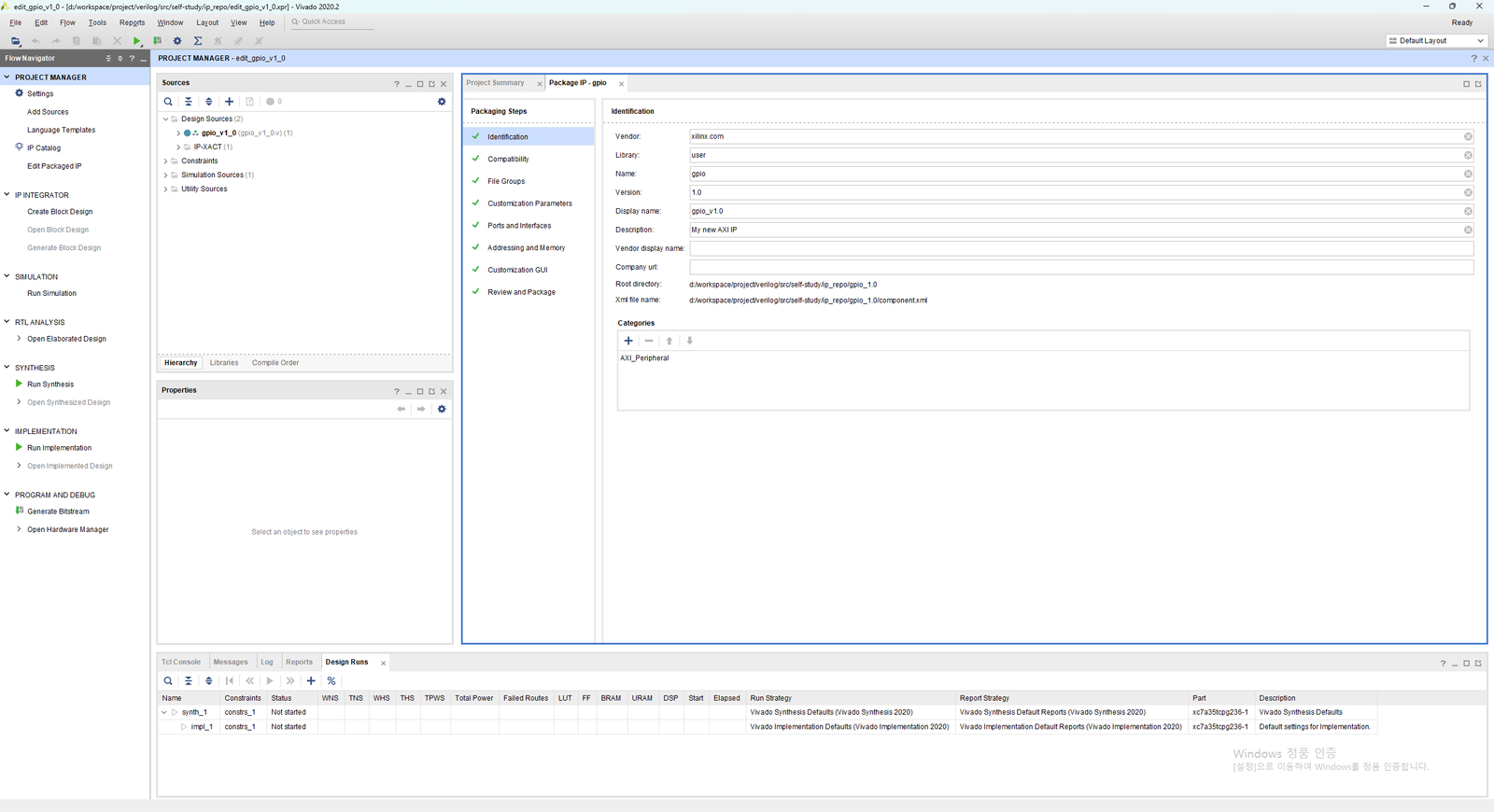

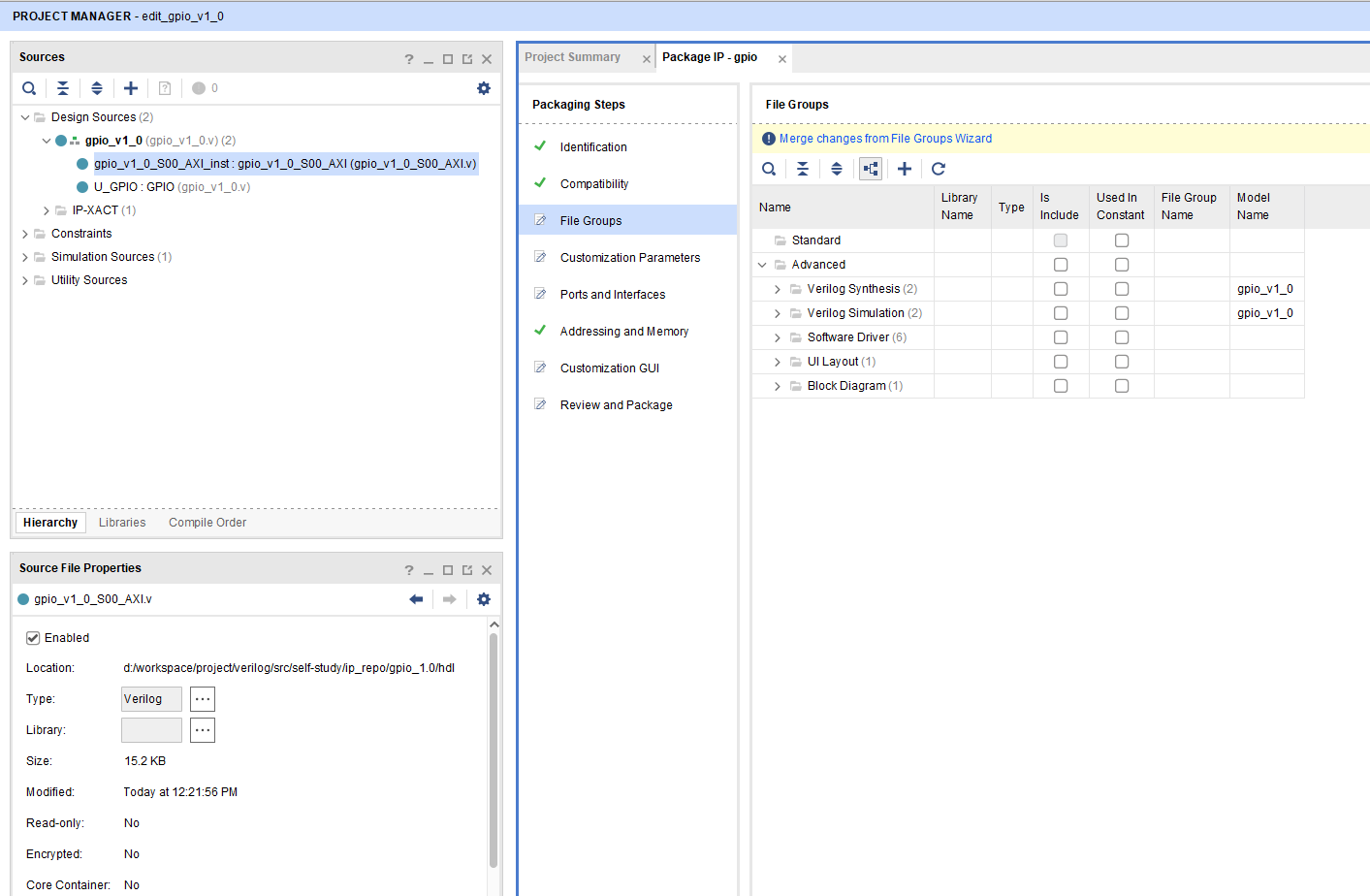

Finish 클릭 후 다음과 같은 Vivado 창이 뜨게 된다.

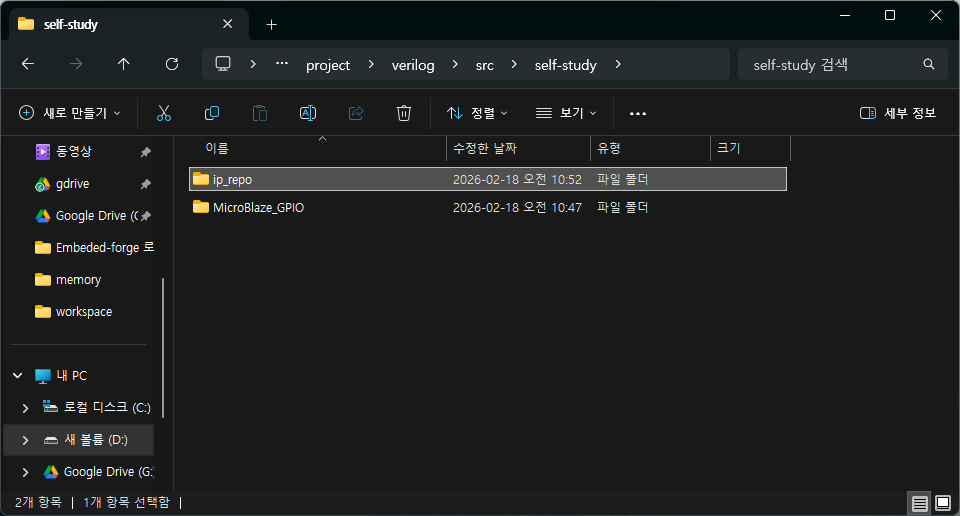

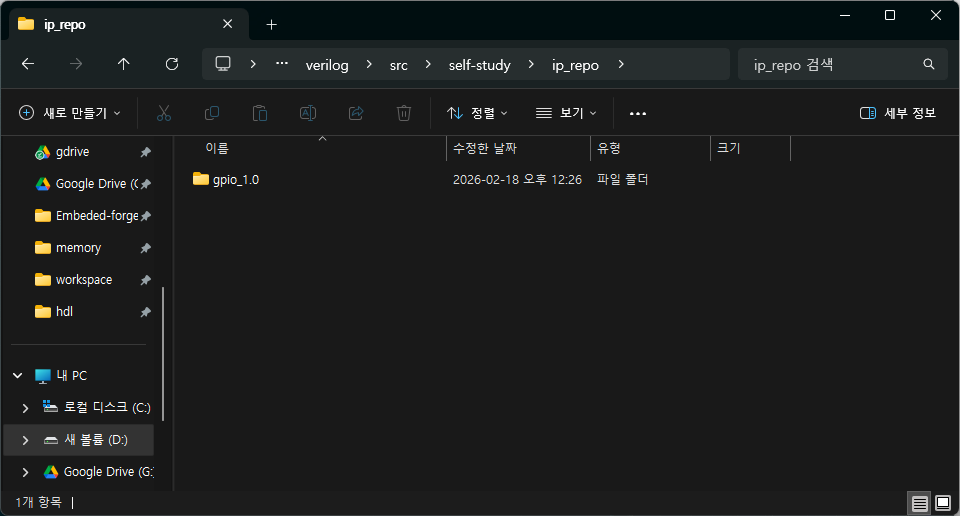

파일탐색기를 열어서 프로젝트의 상위 경로에 들어가보면 ip_repo 폴더가 생긴 것을 확인할 수 있다.

앞으로 이 경로에 ip들을 작업하여 담는 것이 목표이다.

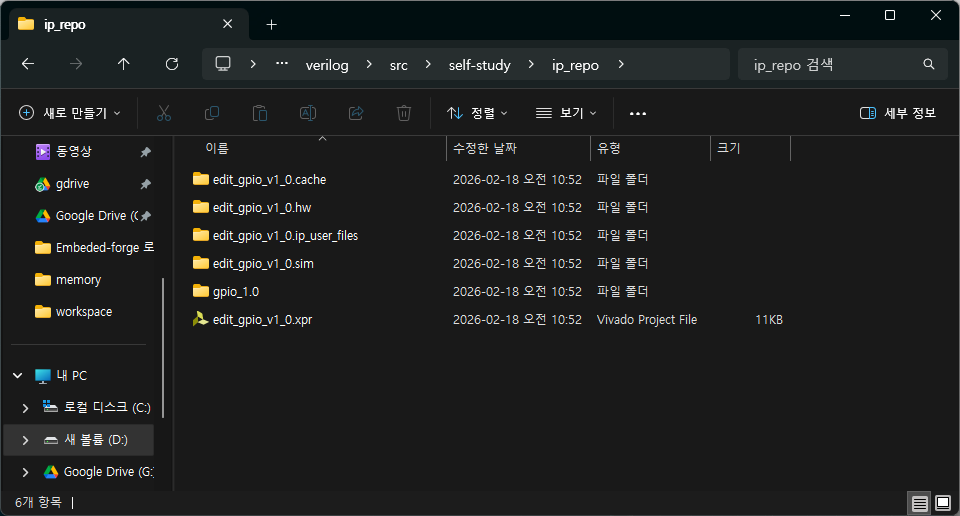

폴더를 들어가보면 다음과 같이 현재 편집중인 vivado 프로젝트가 있는 것을 확인할 수 있다.

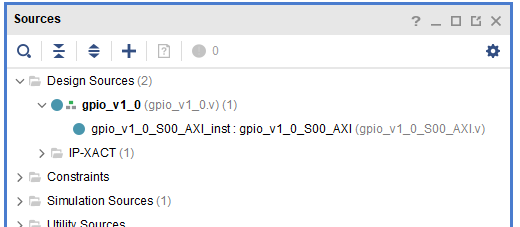

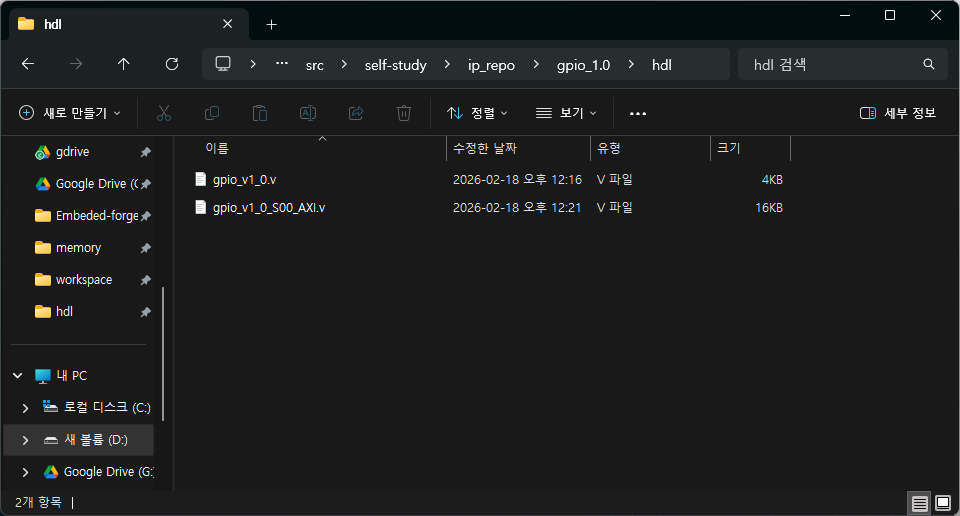

기본 생성 HDL 코드 위치

Vivado 프로젝트에서 이 파일을 열어보면 되고, 이곳을 수정하면 된다

gpio_v1.0.v는 탑으로 잡혀있는 모듈이고, gpio_v1_0_S00_AXI.v는 순수 AXI Slave + 레지스터 모듈이다.

소스코드를 첨부하면 파일이 너무 길어지기 때문에, 나중에 별도의 포스팅으로 설명하도록 하겠다.

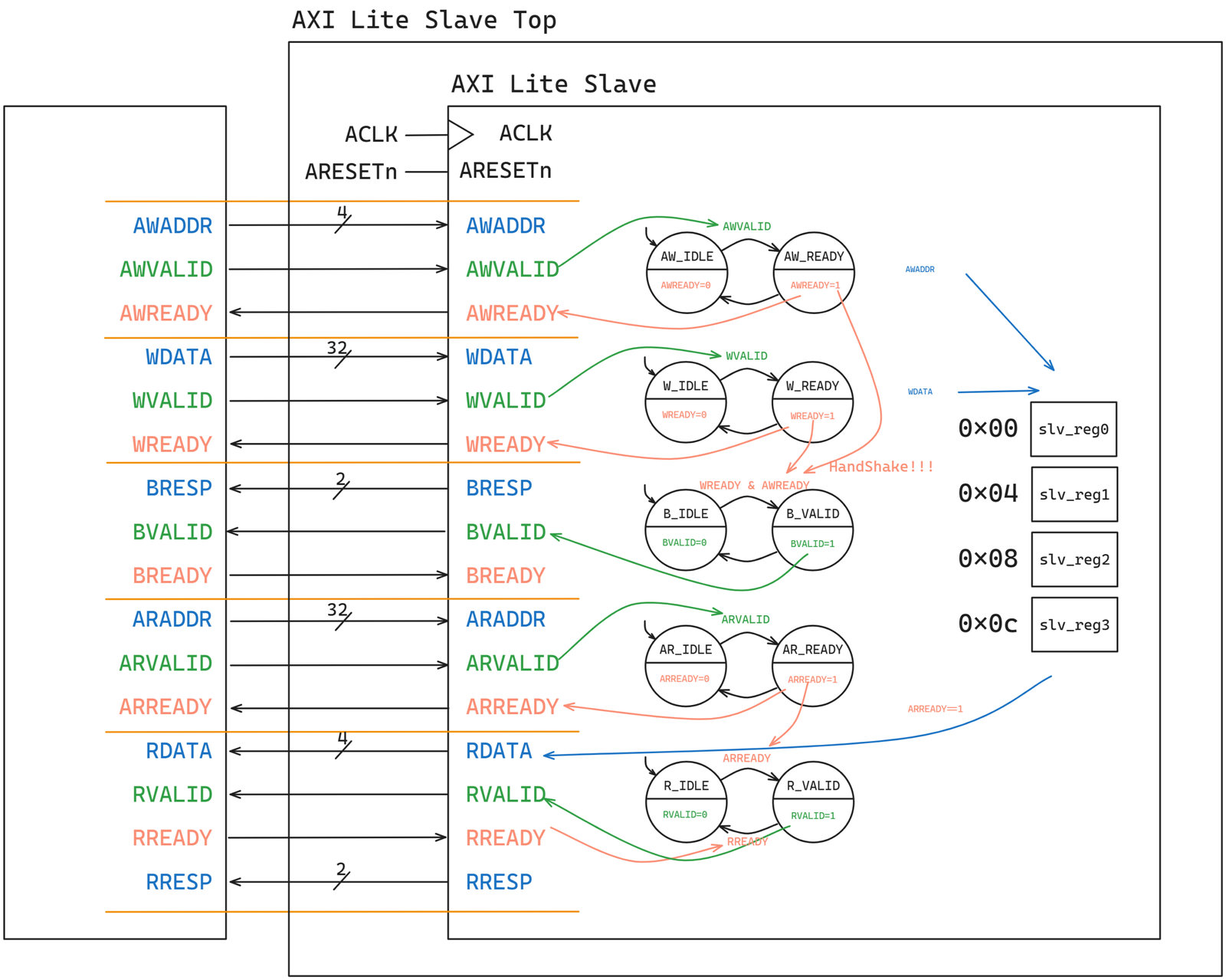

기본 생성 HDL 코드 다이어그램

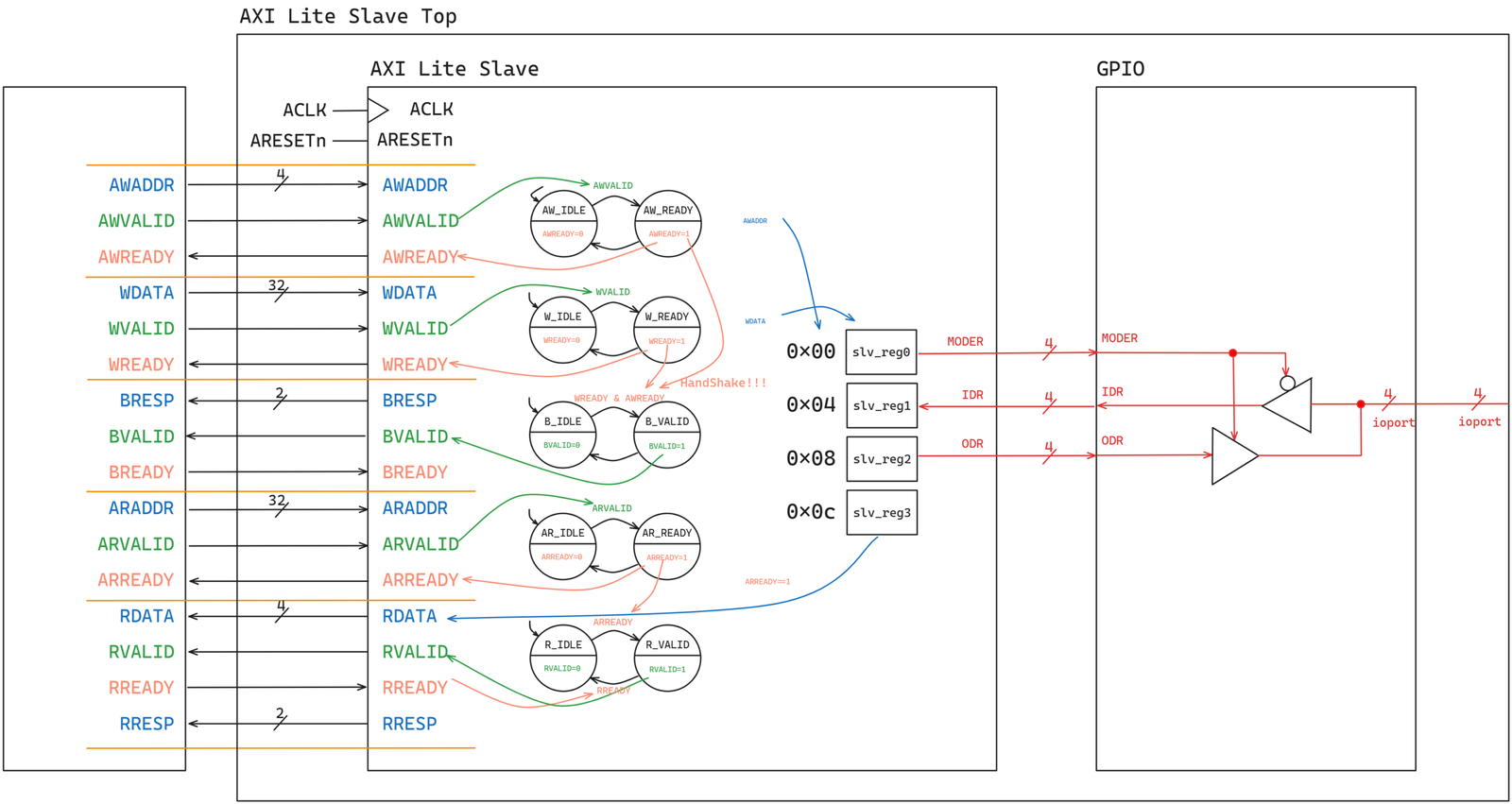

소스 코드를 다이어그램으로 나타내면 다음과 같다.

AXI Lite Slave Top 모듈과 내부 모듈을 각각 입출력과 함께 표시해보았다.

여기까지가 Vivado에서 기본으로 만들어주는 모듈이고, 이 두 모듈을 편집하여 IP를 만들면 된다.

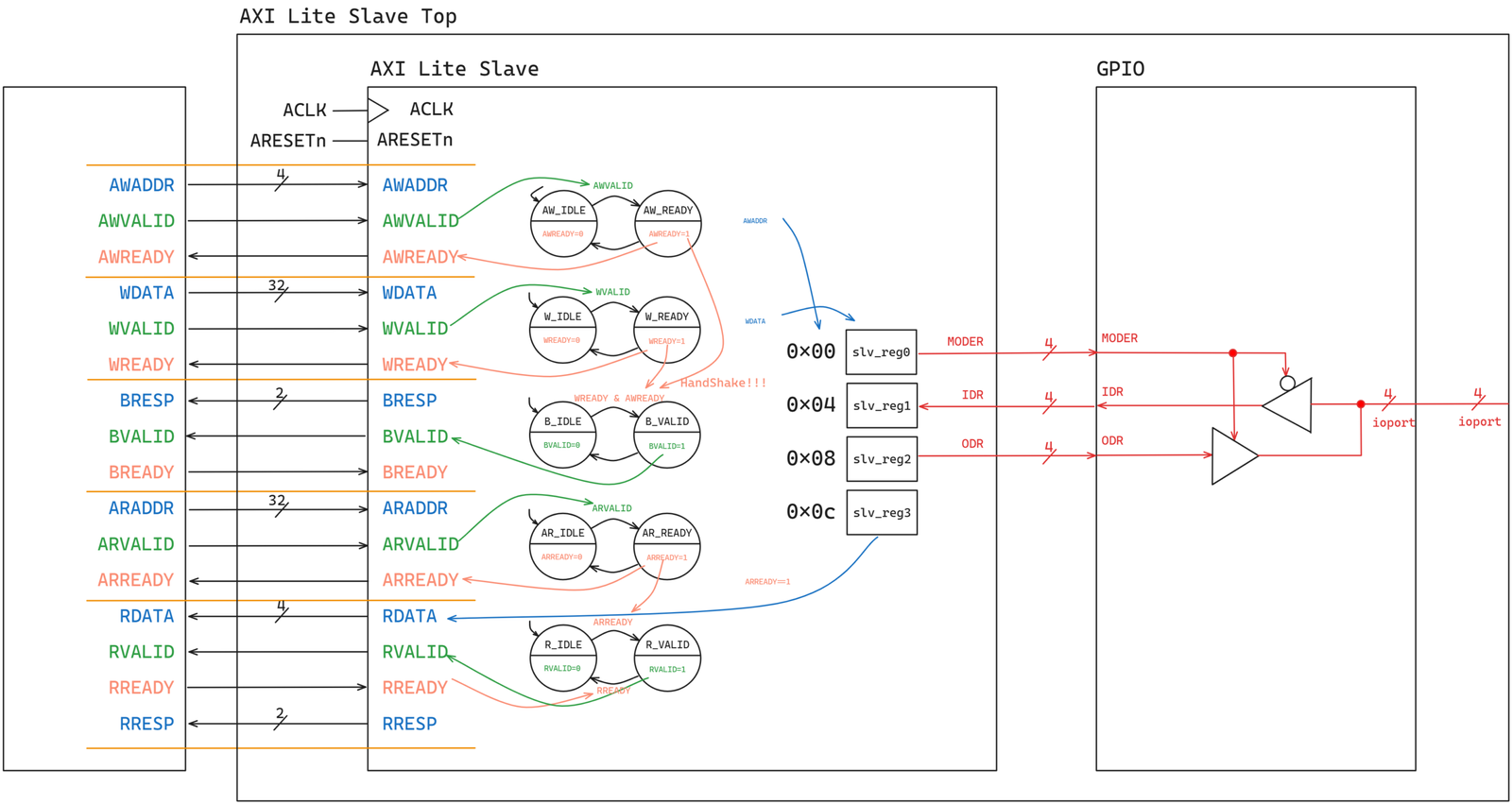

GPIO IP 설계

GPIO IP를 설계 블록 다이어그램은 다음과 같다.

GPIO 동작

GPIO 동작은 다음과 같다.

- slv_reg0을 MODER(MODE Register)로 사용한다.

- MODER에 1이 들어가면 ODR이 활성화되고 IDR은 활성화되지 않는다.

- MODER에 0이 입력되면 IDR은 활성화되고 ODR은 활성화되지 않는다.

- slv_reg1을 IDR(Input Data Register)로 사용한다.

- ioport에 들어온 값을 IDR 포트를 통하여 slv_reg1에 저장한다.

- slv_reg2를 ODR(Output Data Register)로 사용한다.

- slv_reg2에 있는 값을 ODR 포트를 통하여 slv_reg2에 저장한다.

Vivado에서는 최소 레지스터의 개수가 4개이기 때문에 slv_reg3 레지스터가 하나 남았고, 본 프로젝트에서는 사용하지 않았다.

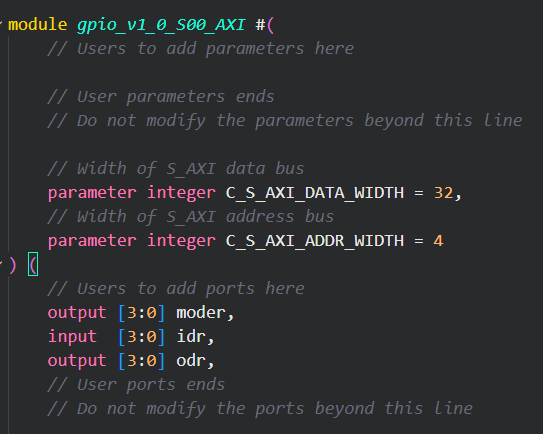

코드 수정

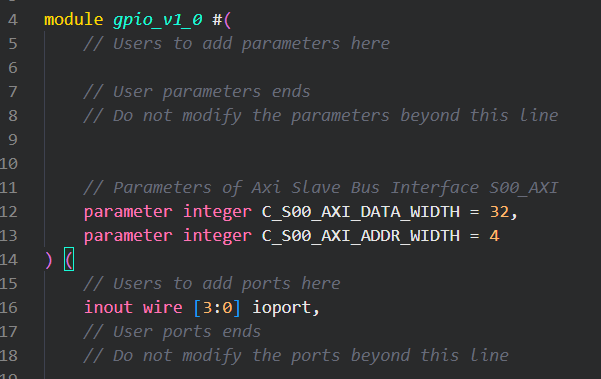

gpio_v1_0_S00_AXI 모듈에서 moder, idr, odr 포트를 추가하였다.

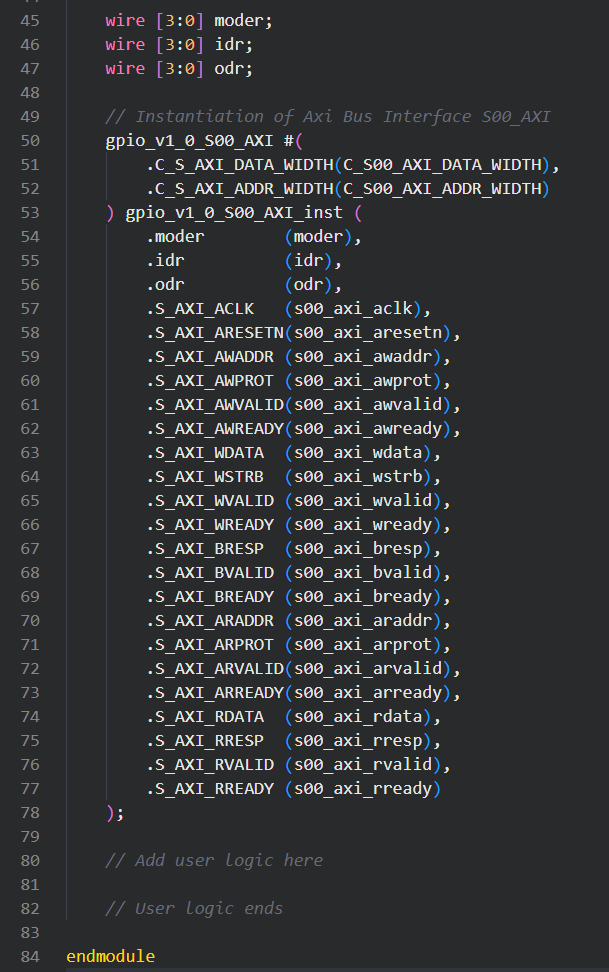

gpio_v1_0_S00_AXI 모듈의 포트가 달라졌으므로 탑 모듈에서 모듈을 수정하고 와이어를 할당해주었다.

탑모듈에서도 포트 선언을 해주었다.

input과 output을 모두 해야 하므로 inout으로 설정하였다.

탑모듈 아래에 위와같이 GPIO 모듈을 만들고 인스턴스화 해주었다.

그리고 아까 할당했던 와이어를 연결하였다.

GPIO 모듈의 경우 generate 구문을 사용하여 4개만큼 반복하였고,

moder에 따라 ioport의 경우는 odr 또는 High-Impedence를 선택하고

idr의 경우는 High-Impedence와 ioport를 선택하도록 하였다.

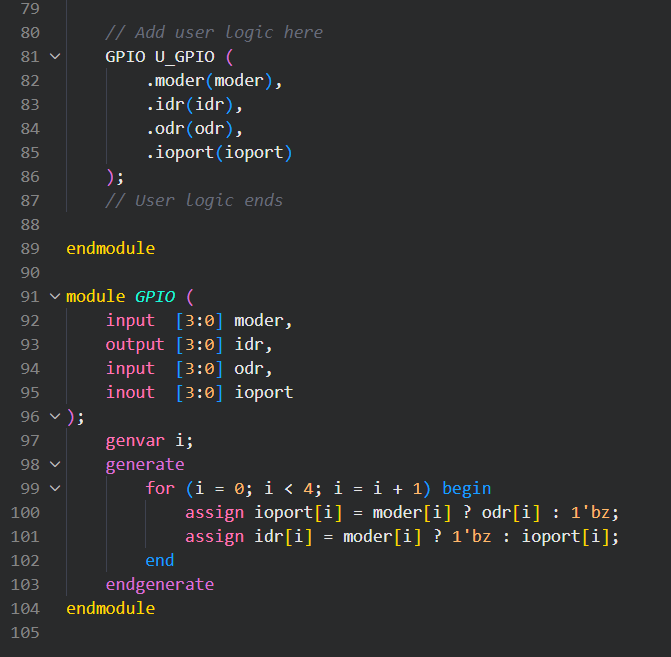

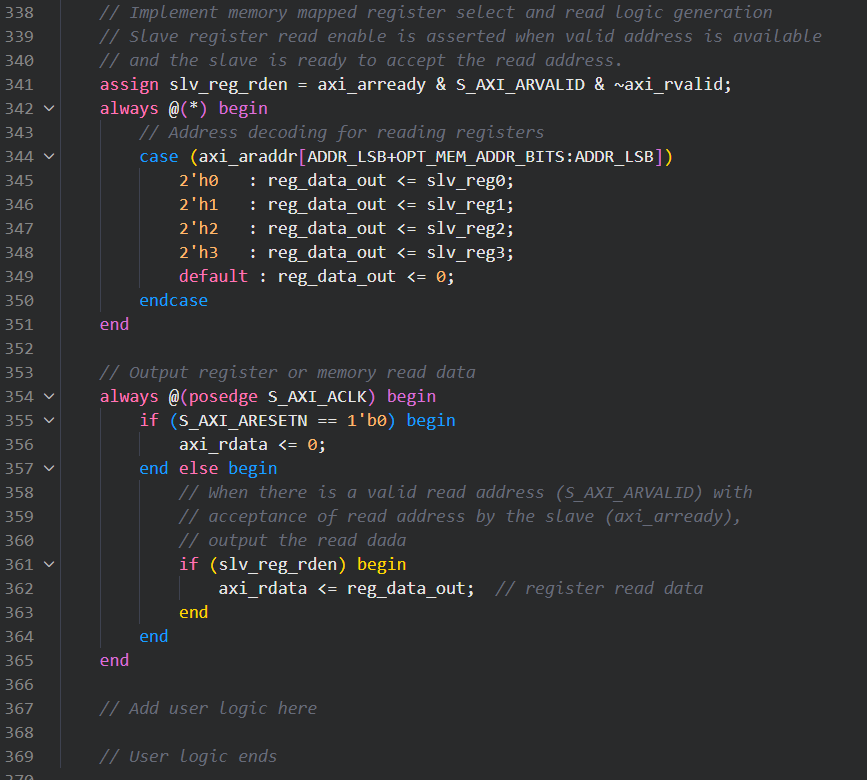

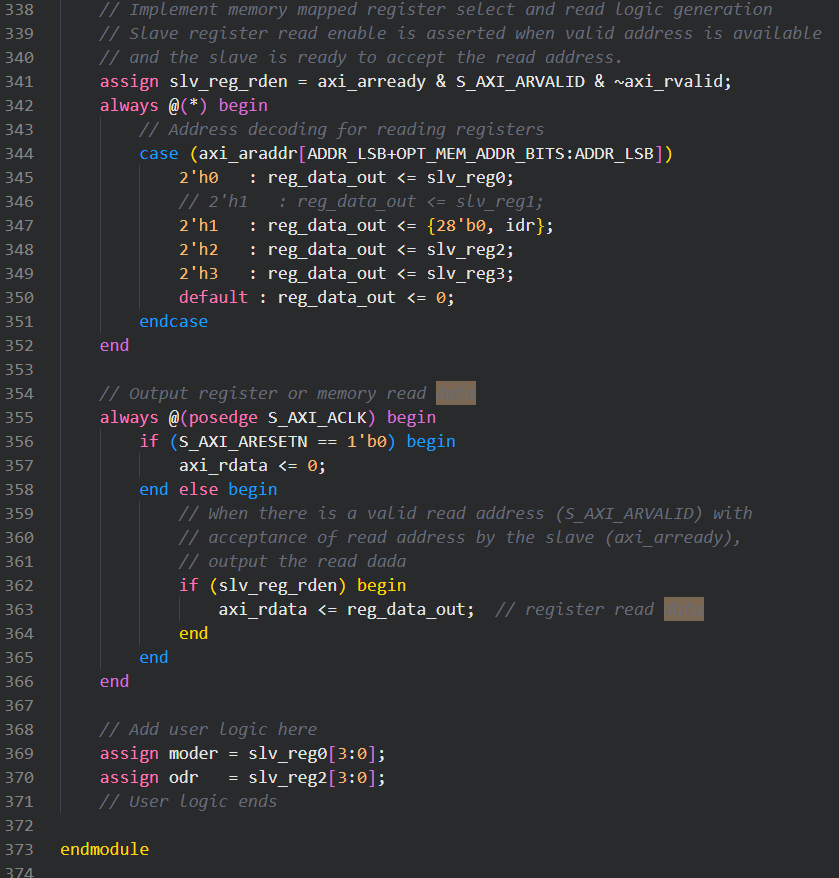

그리고 슬레이브 모듈에서도 입출력을 할당해줘야 하는데,

위와 같이 되어있는 것을 아래와 같이 바꾸었다.

slv_reg1에서 읽어들이던 것을 inout에서 읽어들이도록 바꾸었고,

출력을 assign을 이용하여 slv_reg0와 slv_reg2에서 출력하도록 할당해주었다.

이렇게 수정을 완료한 후 저장한다.

IP Re-Package

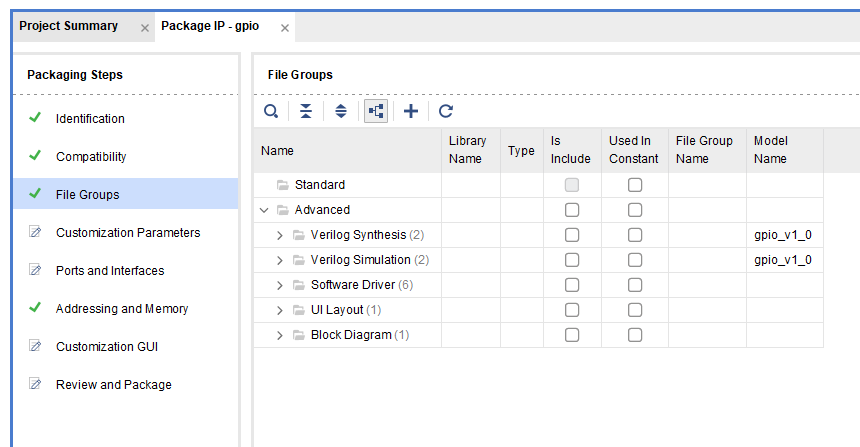

코드를 수정한 후 vivado를 다시 보게 되면 원래는 모두 체크표시되어있었던 게 체크 표시가 풀리게 된다.

현재 체크표시가 풀린 것 중 하나인 File Groups를 클릭한 상태이고,

파란색 글씨로 Merge changes from File Groups Wizard라고 떠있다.

Merge change를 누르면 체크표시가 다시 뜨게 된다.

이런 식으로 하나 하나 모두 Merge Change를 눌러주면 된다.

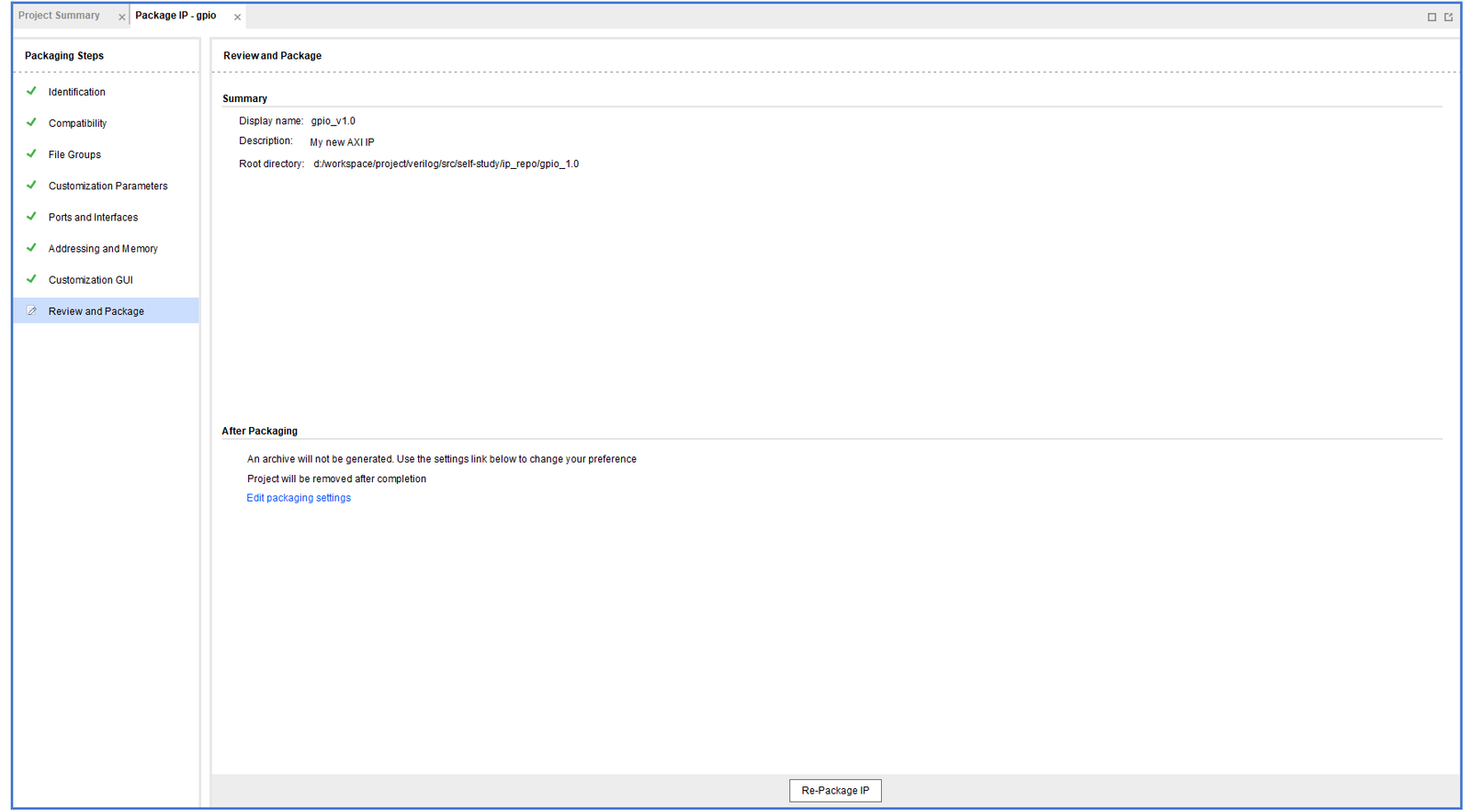

그리고 마지막 Review and Package에는 아래에 Re-Package IP 버튼이 있는데 이것을 눌러주면 된다.

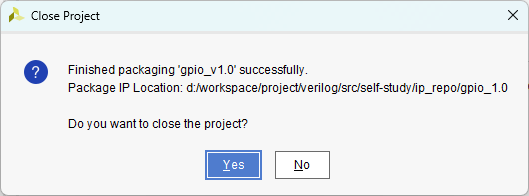

이렇게 뜨는데 어차피 IP 수정은 끝났으니 Yes 눌러서 닫으면 된다.

IP 패키징 후 Driver 버그 유발사항 수정

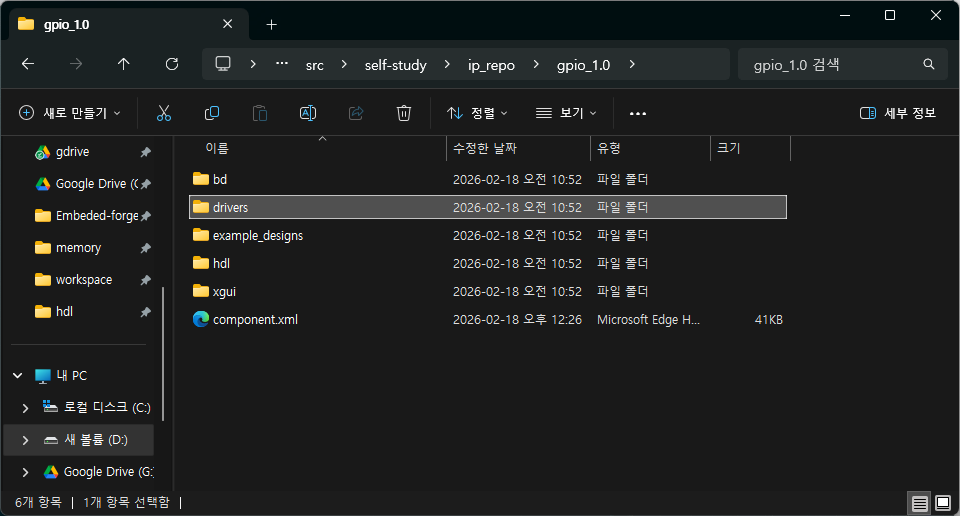

이렇게 완료됐으면 ip_repo 경로를 들어가면 다음과 같이 나온다. 한번 둘러보자.

폴더를 들어가게 되면 다음과 같이 각종 IP 파일들이 나오게 된다.

이 중 hdl 폴더를 들어가게 되면 다음과 같이 기존에 작성했던 코드들이 존재한다.

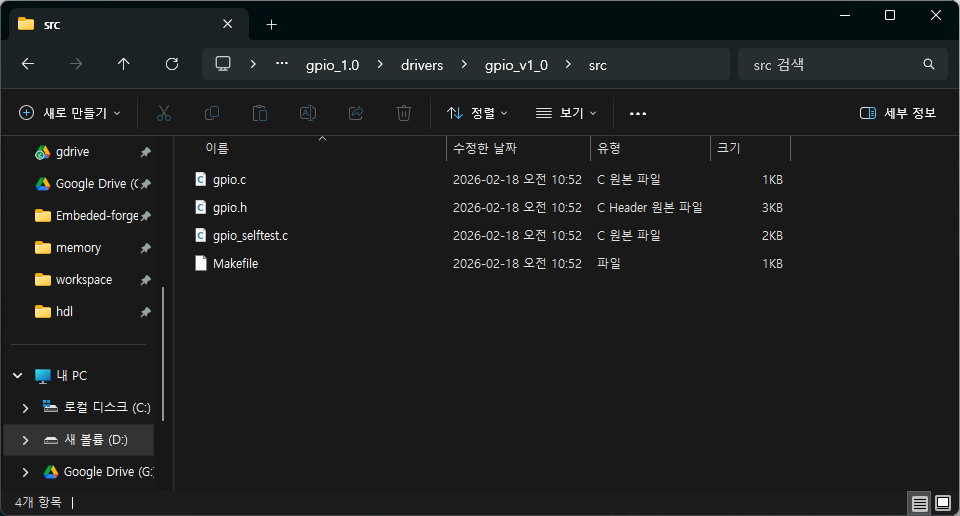

drivers 폴더에 들어가게 되면 다음과 같이 vitis에서 사용하는 C 드라이버가 나오게 된다.

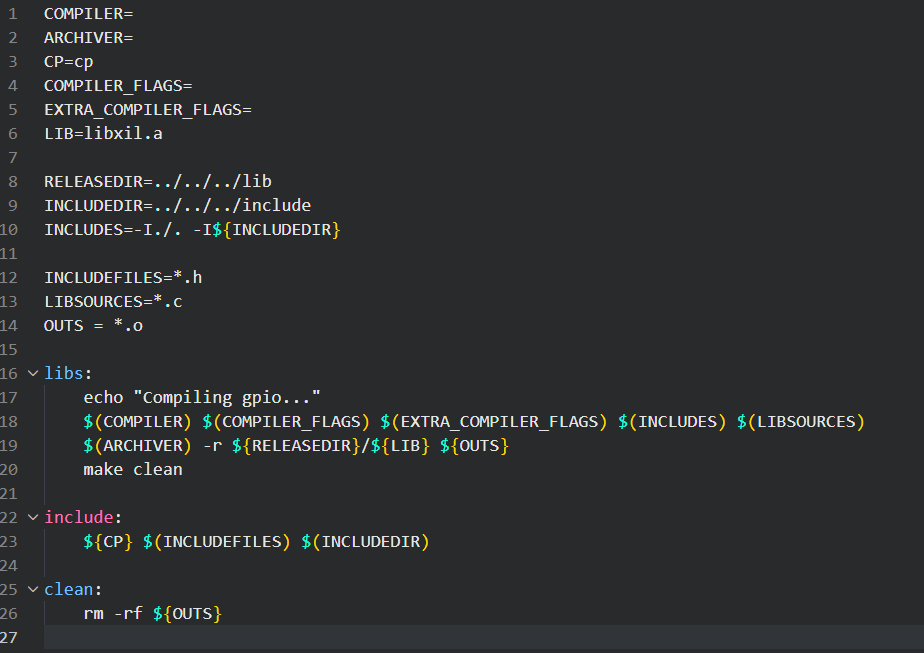

이 중에 Makefile을 열어보면

이렇게 뜨는데

INCLUDEFILES=*.h

LIBSOURCES=*.c

OUTS = *.o

이 부분을 아래와 같이 바꾸어준다.

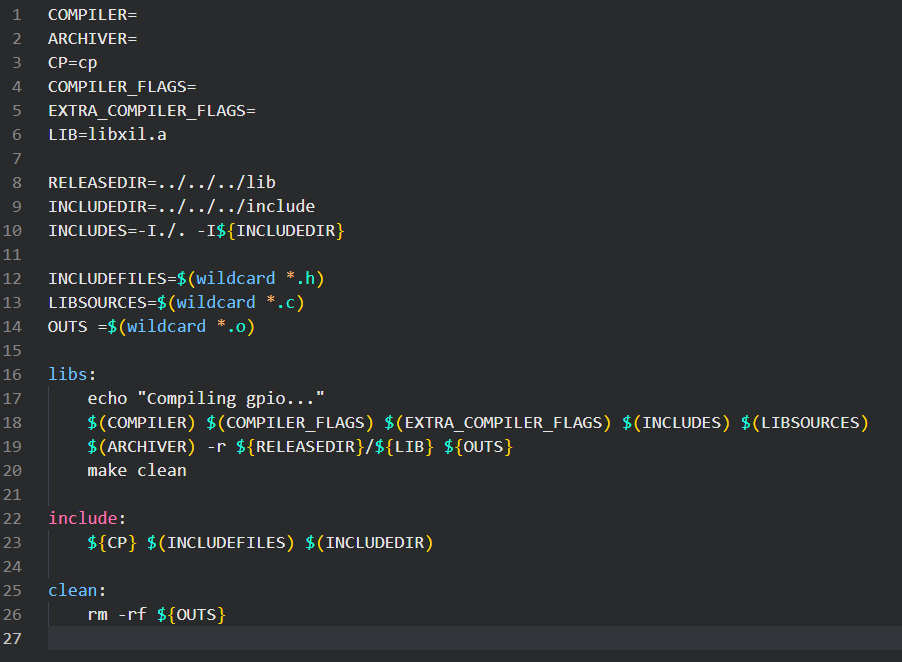

INCLUDEFILES=$(wildcard *.h)

LIBSOURCES=$(wildcard *.c)

OUTS =$(wildcard *.o)

이렇게 저장만 해주고 나오면 된다.

결론

이것으로 GPIO IP 설계를 마무리하였고, MicroBlaze에서 불러올 수 있는 상태가 되었다.

다음 포스팅에서 MicroBlaze에서 SW 빌드까지 진행해보도록 하겠다.