약 3분 소요

SPI란?

=> 시리얼 통신의 한 종류로서, 동기식 전이중 방식의 고속 프로토콜.

SPI 특징 및 장단점

- 동기식 프로토콜

- => 클럭 기반으로 동작하기 때문에 정확하게 동작 가능

- => 고속 가능

- 1:N 통신 가능

- 전이중(Full Duplex) 방식

- 동시 송수신 가능

- 설계복잡도가 높지 않다

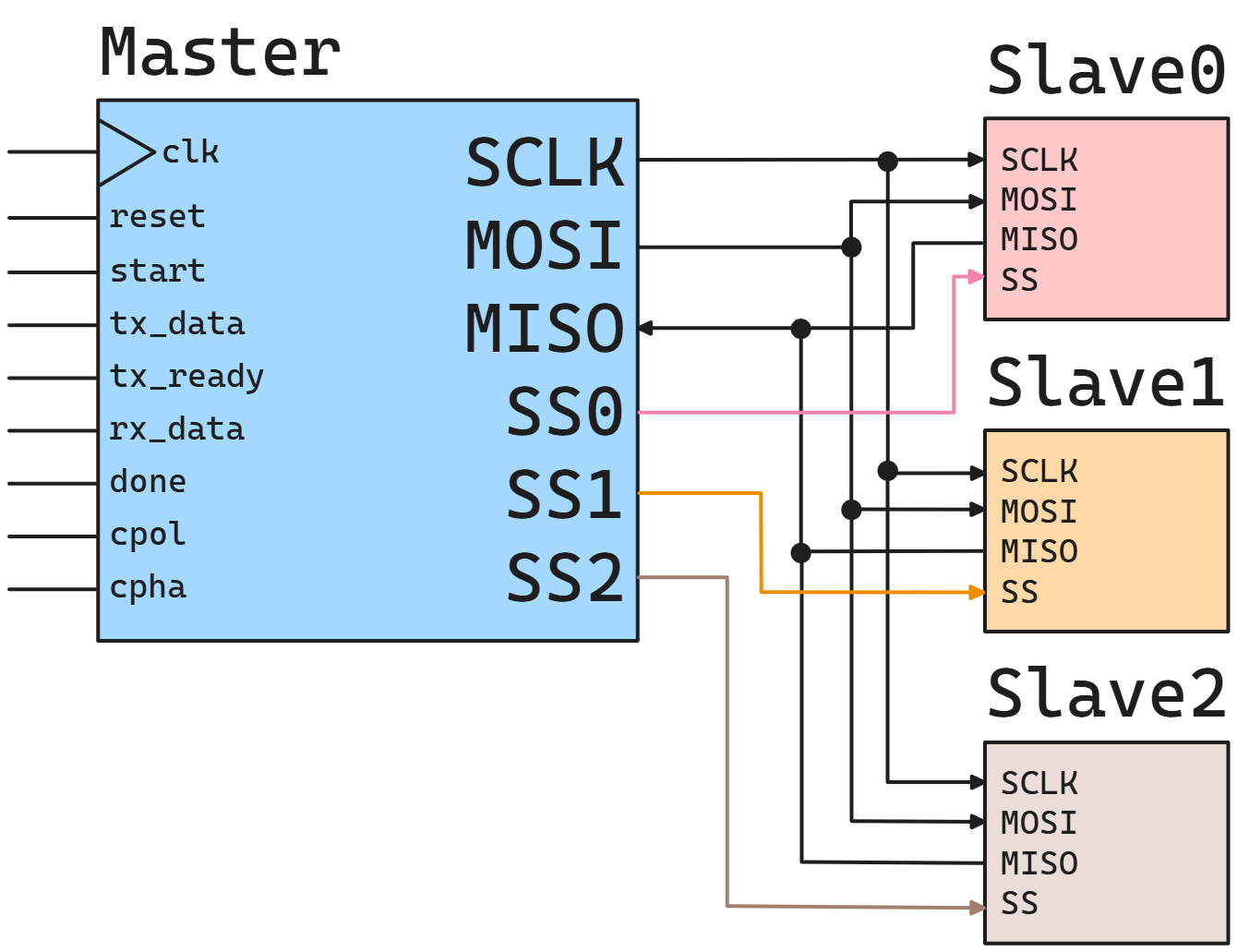

SPI 신호(SCLK, MOSI, MISO)

기본적으로 SPI는 SCLK, MOSI, MISO가 공통으로 연결된다.

그리고 SS (또는 CS)라고 하는 셀렉터를 통해 Slave를 선택하게 된다.

SS는 Active Low로 동작하기 때문에 Low로 떨어트려줘야 해당하는 Slave가 선택이 된다.

또한 Slave는 한 번에 하나만 선택이 되며, 2개 이상의 슬레이브가 선택되면 안된다.

SPI 동작 원리(서술)

일단 SPI 통신의 기본이 되는 프로토콜은 다음과 같다.

마스터의 중요한 역할 중 하나가 클럭을 생성하는 기능이다.

로직 애널라이저로 파형 확인이 수월하도록 SCLK를 1MHz로 설계하였다.

CPOL/CPHA 4가지 모드 동작 사항

기본적으로 CPOL과 CPHA에 대해서 정리하면 다음과 같다.

- CPOL : 클럭 idle 상태

- CPOL=0: idle이 Low → 첫 번째 엣지가 상승, 두 번째 엣지가 하강

- CPOL=1: idle이 High → 첫 번째 엣지가 하강, 두 번째 엣지가 상승

- CPHA : 샘플링 시점

- CPHA=0:

- 데이터 로딩: CS_n 시점에 MOSI, MISO 데이터 로딩

- 샘플링: 첫 번째 엣지에서 샘플링

- CPHA=1:

- 데이터 로딩: 반주기 뒤에 MOSI, MISO 데이터 로딩

- 샘플링: 두 번째 엣지에서 샘플링

- CPHA=0:

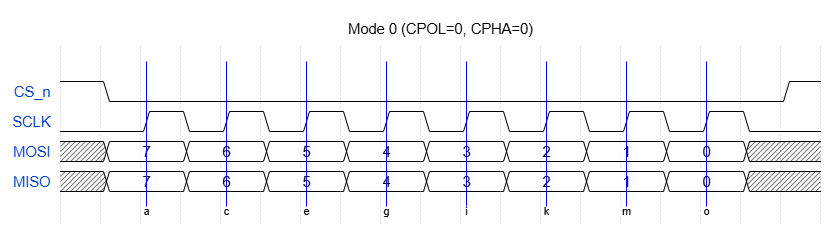

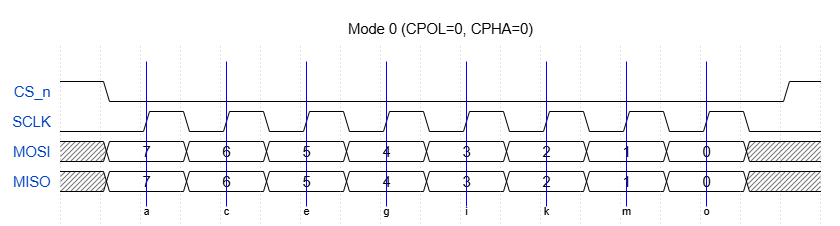

MODE0 (CPOL=0, CPHA=0)

- CS_n이 LOW로 내려가면서 Chip Select

- CPHA=0이므로 MOSI, MISO에 바로 데이터 로딩

- CPOL=0이므로 SCLK idle이 Low → 첫 번째 엣지는 상승 엣지 → 두 번째 엣지는 하강 엣지

- CPHA=0이므로 첫번째 엣지인 상승 엣지에서 샘플링

- 8개의 비트에 대해서 모두 반복

- CS_n이 High로 올라감

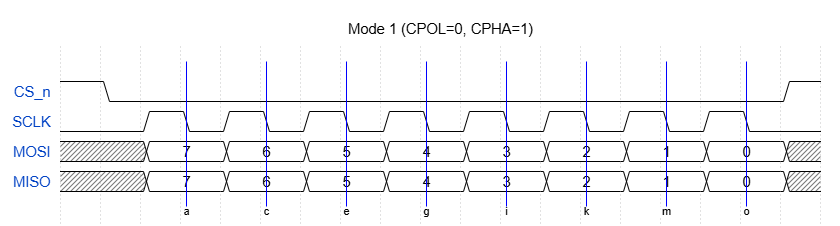

MODE1 (CPOL=0, CPHA=1)

- CS_n이 LOW로 내려가면서 Chip Select

- CPHA=1이므로 MOSI, MISO 반주기만큼 딜레이 후 데이터 로딩

- CPOL=0이므로 SCLK idle이 Low → 첫 번째 엣지는 상승 엣지 → 두 번째 엣지는 하강 엣지

- CPHA=1이므로 두번째 엣지인 하강 엣지에서 샘플링

- 8개의 비트에 대해서 모두 반복

- CS_n이 High로 올라감

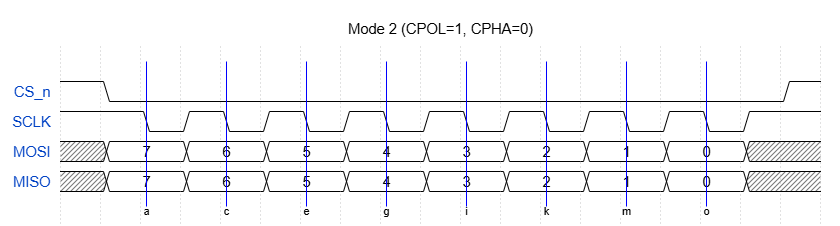

MODE2 (CPOL=1, CPHA=0)

- CS_n이 LOW로 내려가면서 Chip Select

- CPHA=0이므로 MOSI, MISO에 바로 데이터 로딩

- CPOL=1이므로 SCLK idle이 HIGH → 첫 번째 엣지는 하강 엣지 → 두 번째 엣지는 상승 엣지

- CPHA=0이므로 첫번째 엣지인 하강 엣지에서 샘플링

- 8개의 비트에 대해서 모두 반복

- CS_n이 High로 올라감

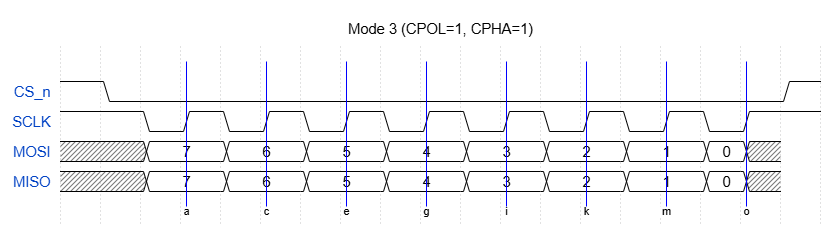

MODE3 (CPOL=1, CPHA=1)

- CS_n이 LOW로 내려가면서 Chip Select

- CPHA=1이므로 MOSI, MISO 반주기만큼 딜레이 후 데이터 로딩

- CPOL=1이므로 SCLK idle이 HIGH → 첫 번째 엣지는 하강 엣지 → 두 번째 엣지는 상승 엣지

- CPHA=1이므로 두번째 엣지인 상승 엣지에서 샘플링

- 8개의 비트에 대해서 모두 반복

- CS_n이 High로 올라감