Serial Communication – SPI 개념

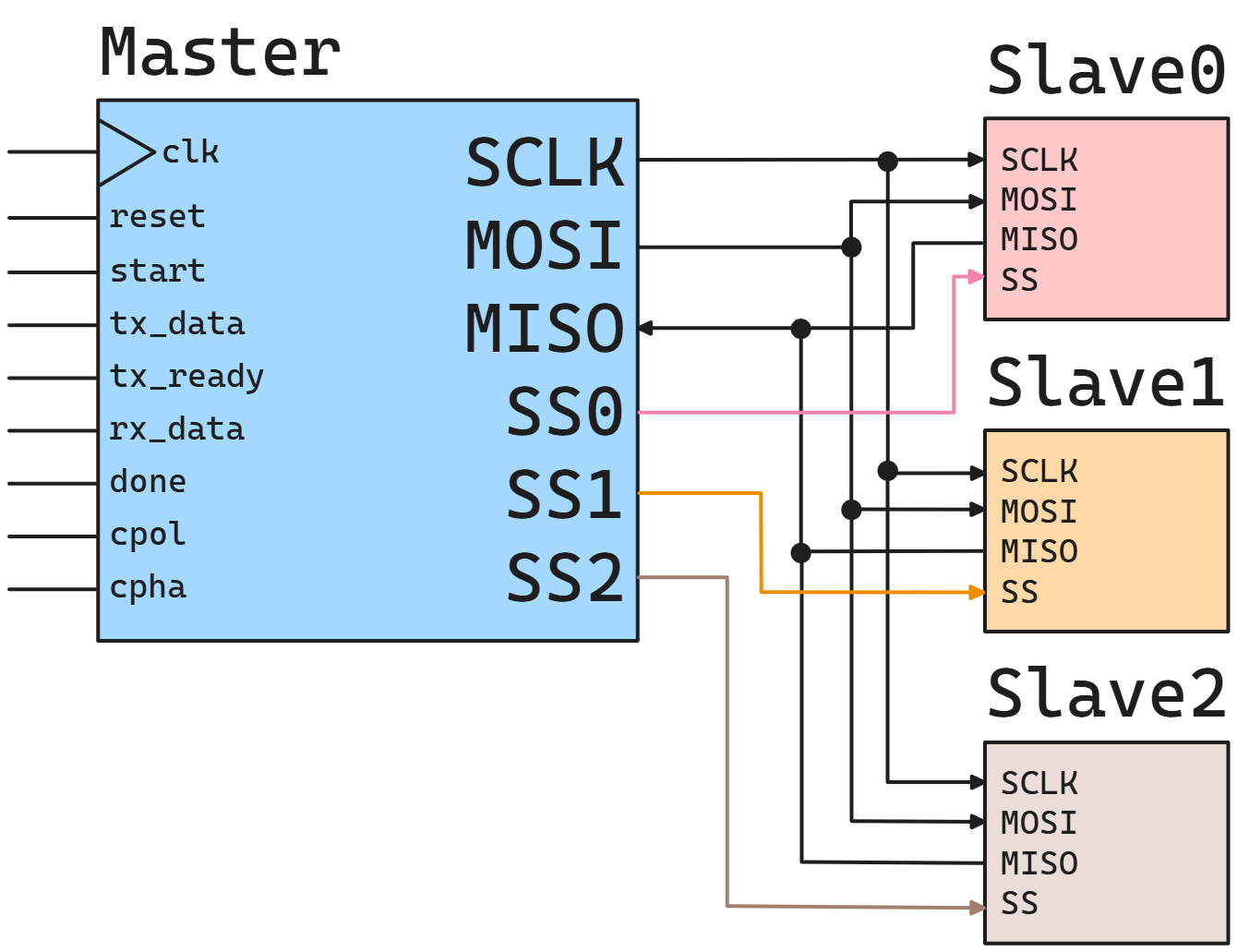

SPI란? => 시리얼 통신의 한 종류로서, 동기식 전이중 방식의 고속 프로토콜. SPI 특징 및 장단점 SPI 신호(SCLK, MOSI, MISO) 기본적으로 SPI는 SCLK, MOSI, MISO가 공통으로 연결된다.그리고 SS (또는 CS)라고 하는 셀렉터를 통해 Slave를 선택하게 된다. SS는 Active Low로 동작하기 때문에 Low로 떨어트려줘야 해당하는 Slave가 선택이 된다.또한 Slave는 한 번에 하나만 선택이 되며, 2개 이상의 슬레이브가 … Read more