약 5분 소요

개요

지난 포스팅(AMBA AXI – GPIO IP 설계(1))에 이어서, GPIO IP를 MicroBlaze에서 동작시키기 위해 Vitis로 올리는 작업을 해보겠다.

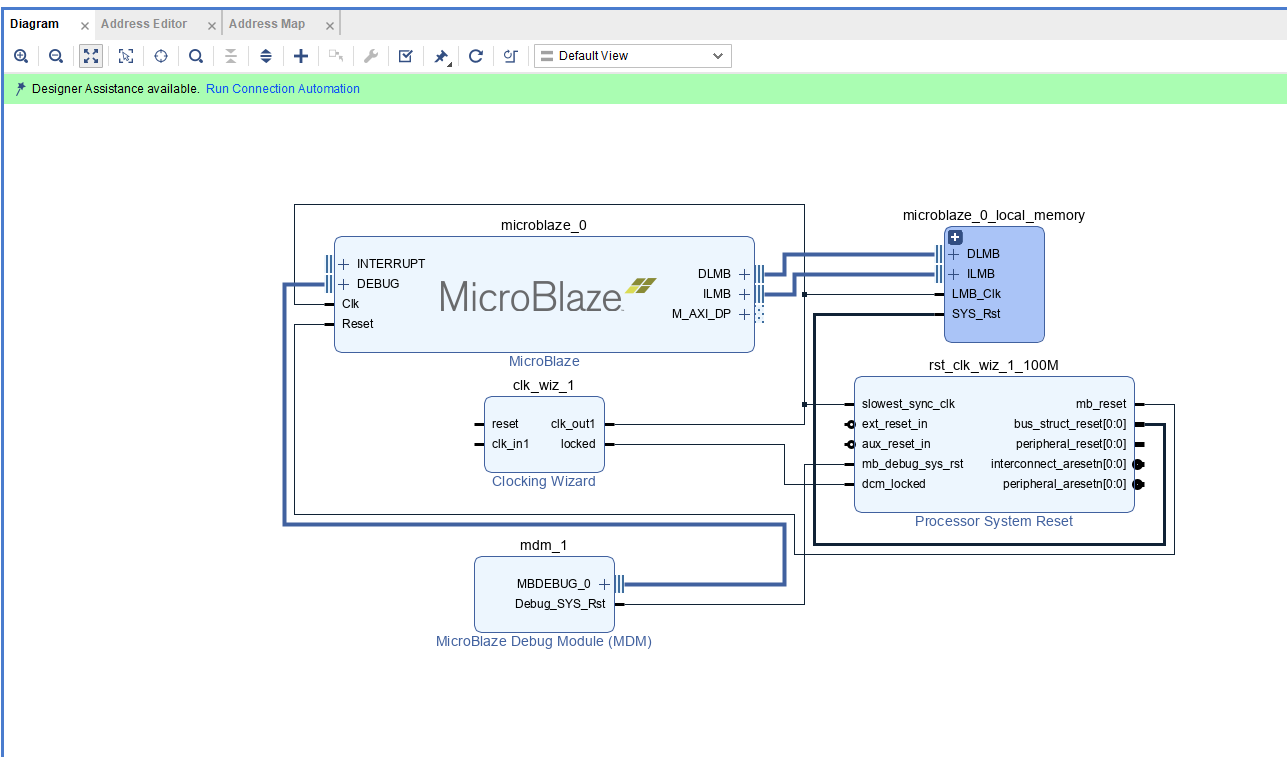

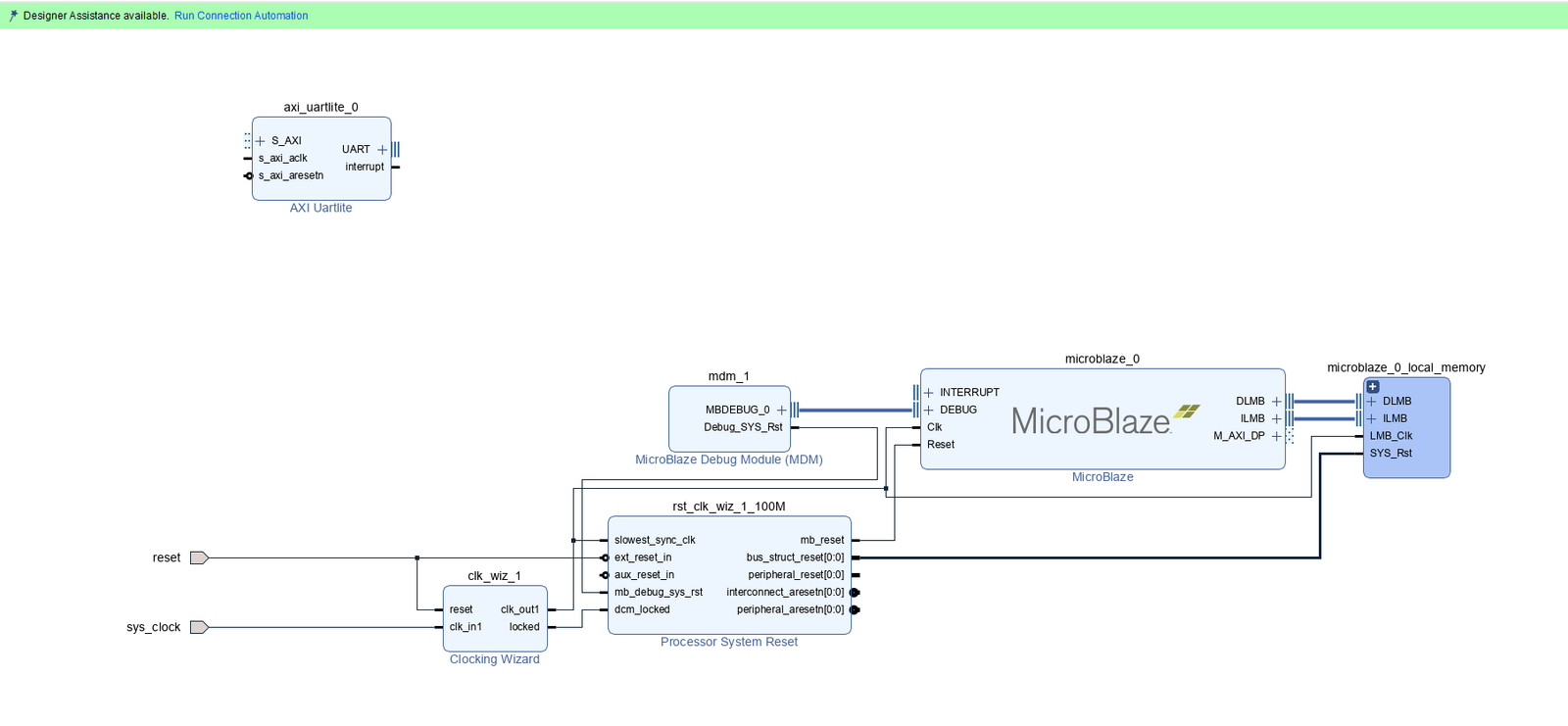

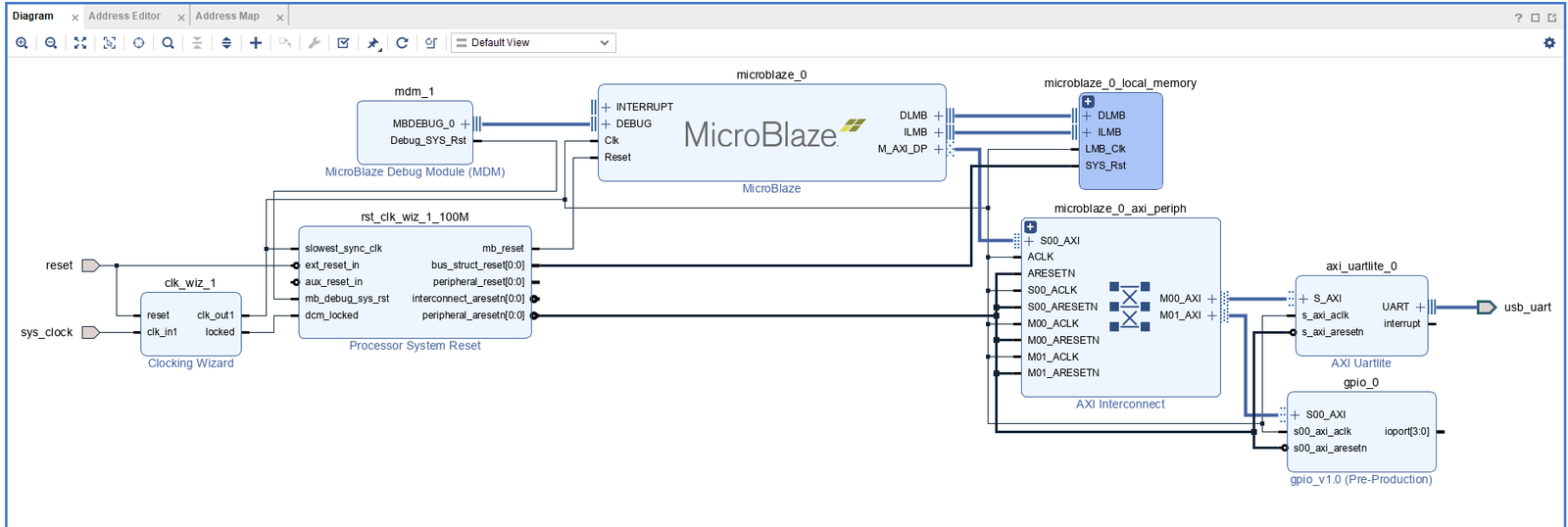

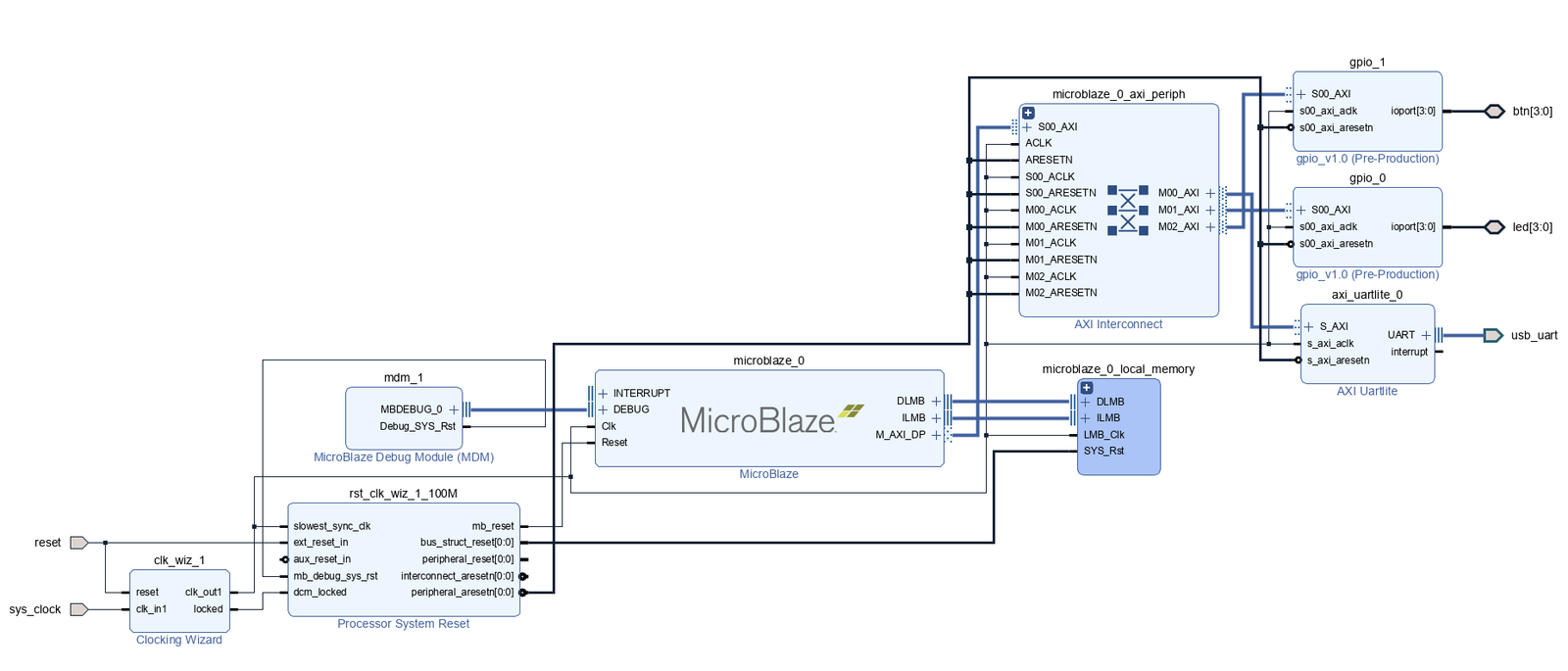

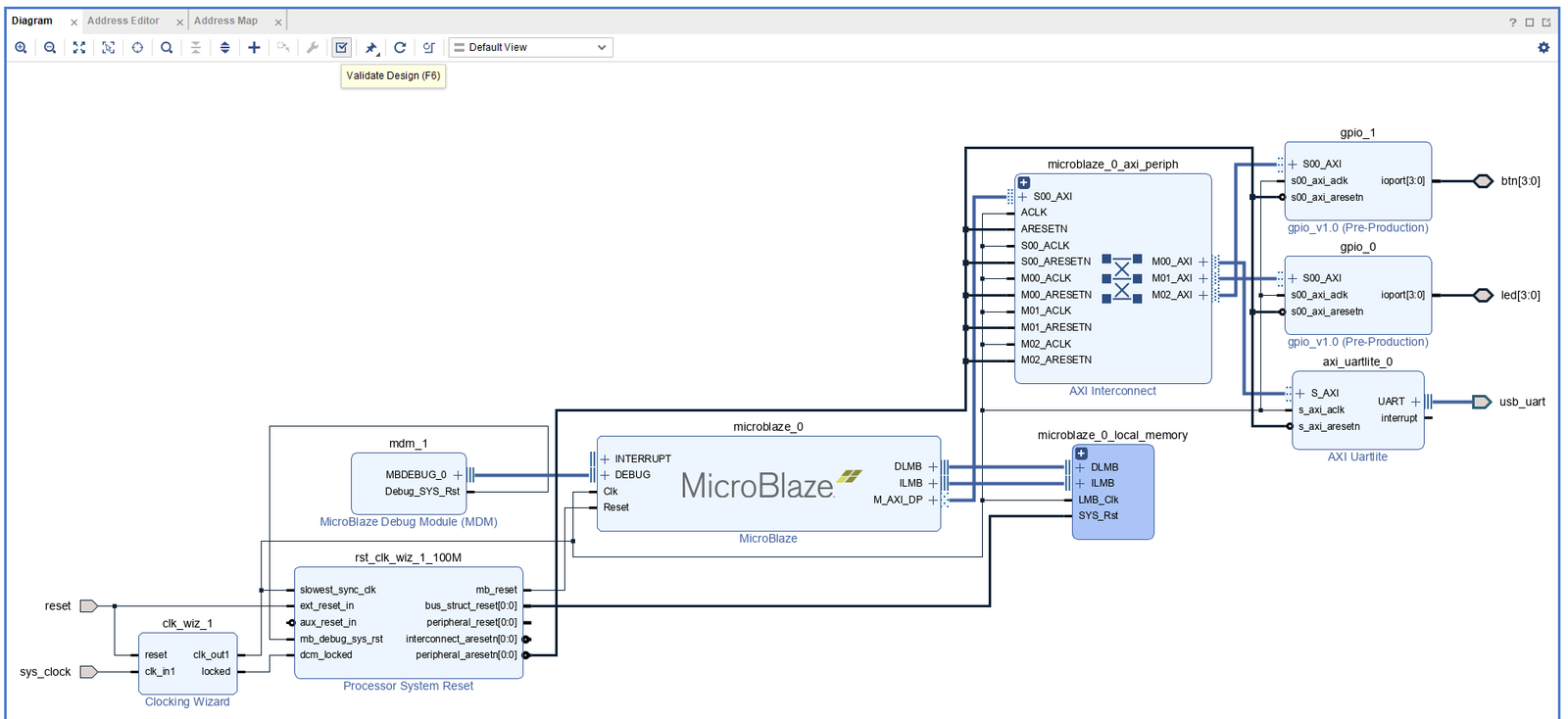

Block Design

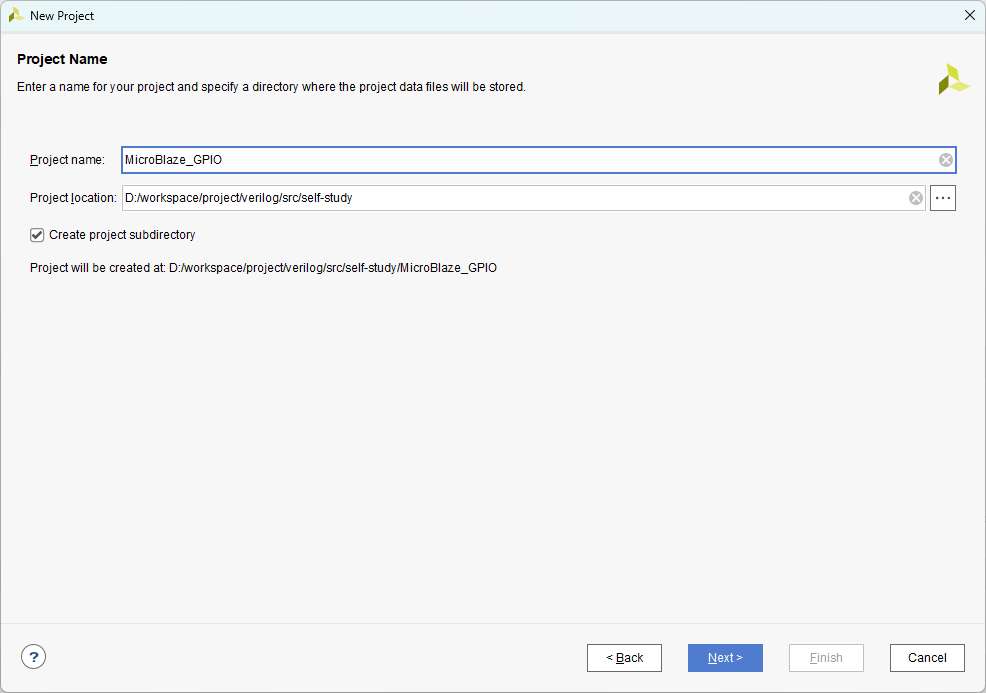

MicroBlaze용 Vivado 프로젝트 생성

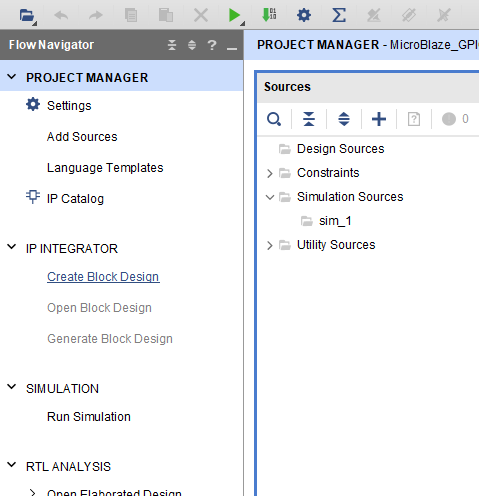

Block Design 진행

Create Block Design 클릭

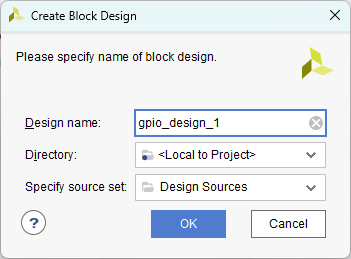

Design name 마음대로 입력

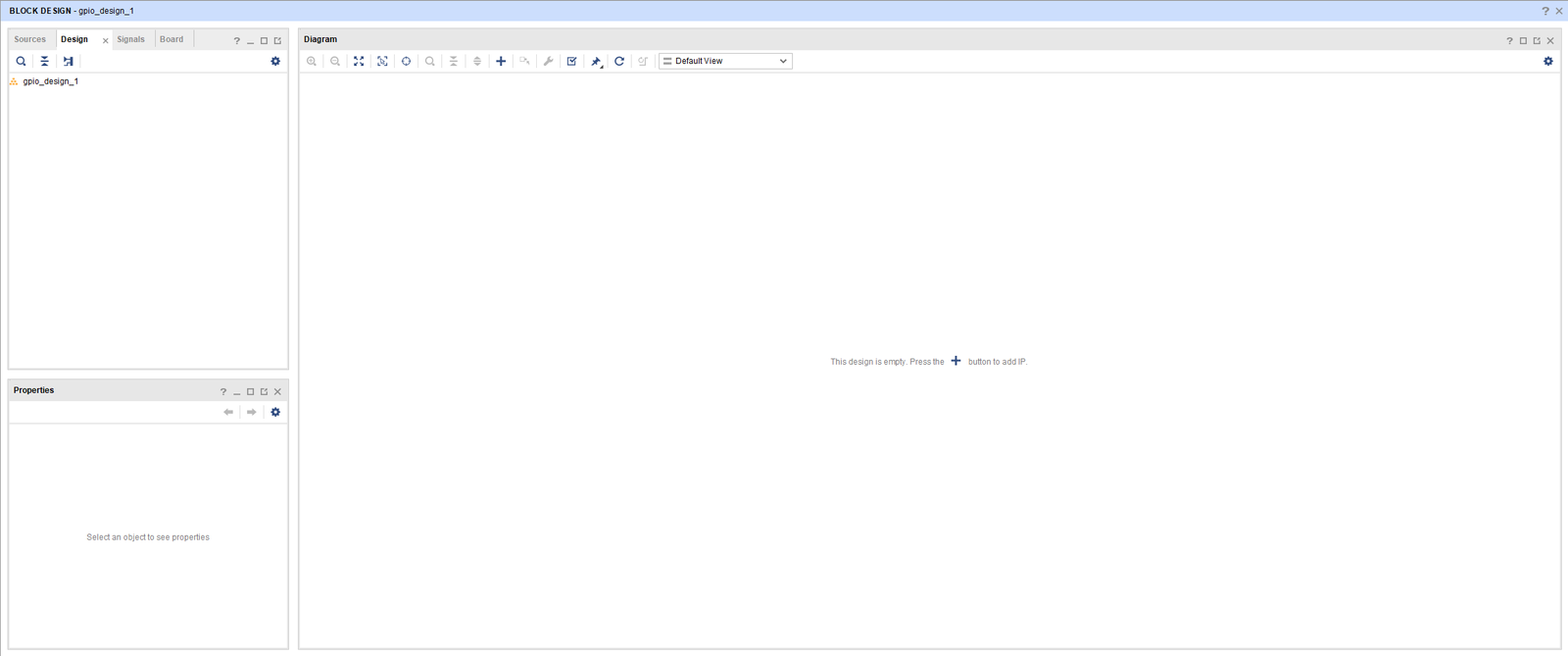

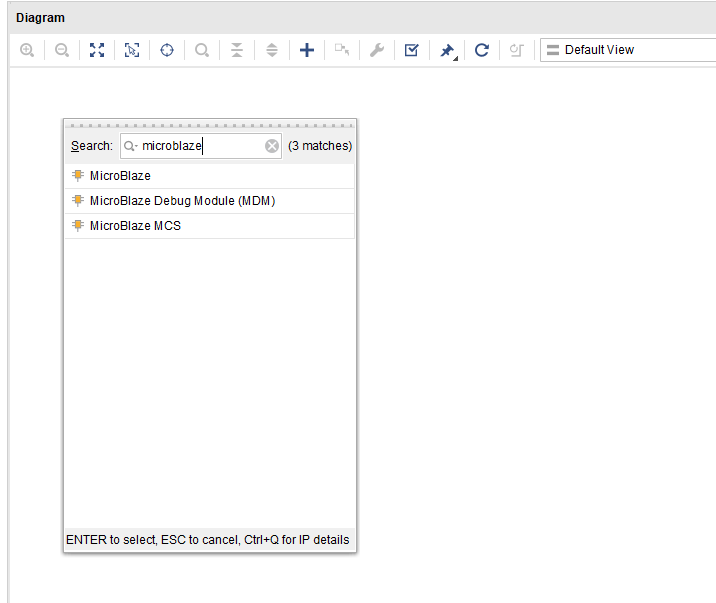

MicroBlaze 추가

Diagram 탭에서 + 버튼 클릭

microblaze 검색 후 첫번째 선택

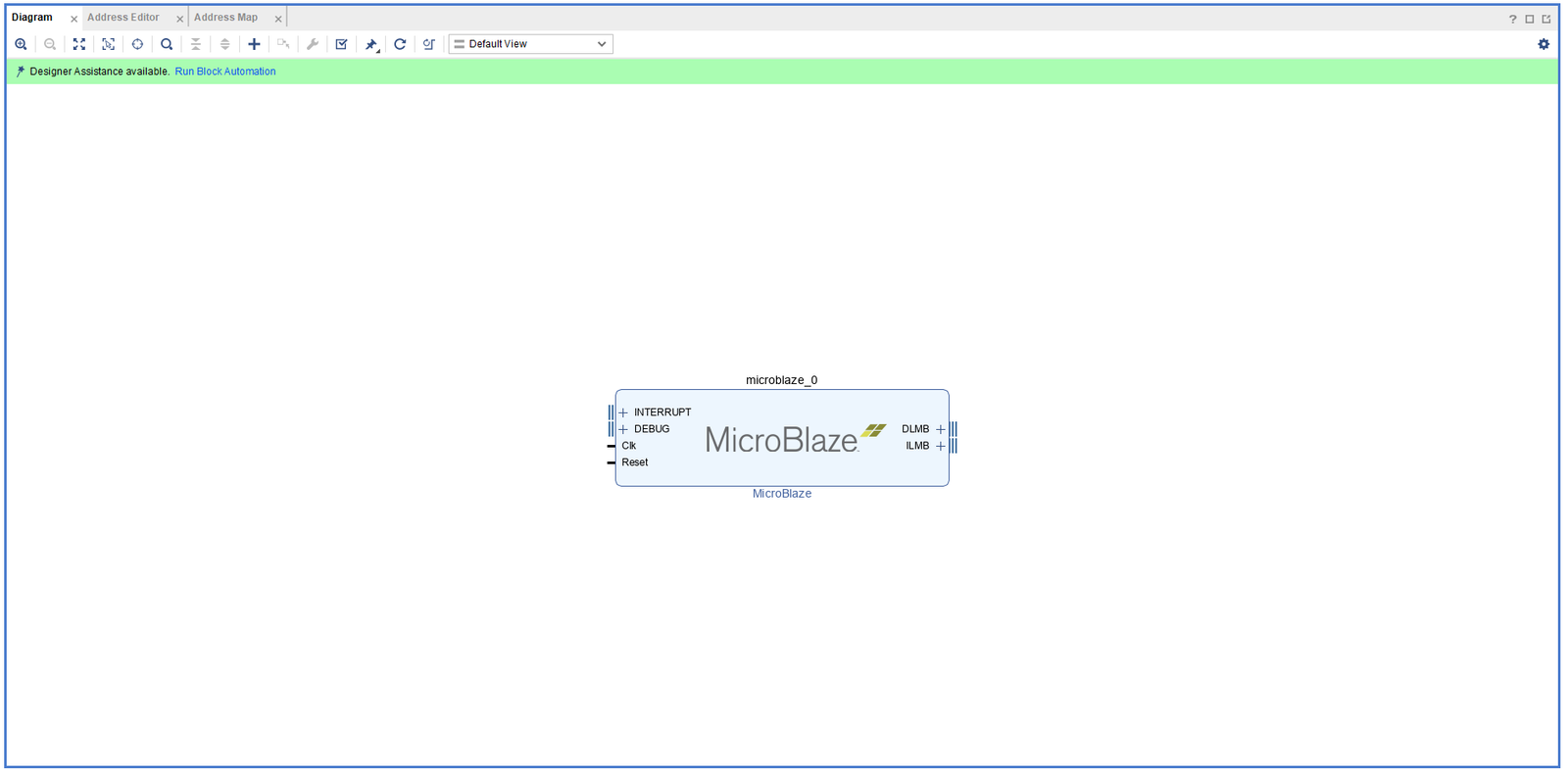

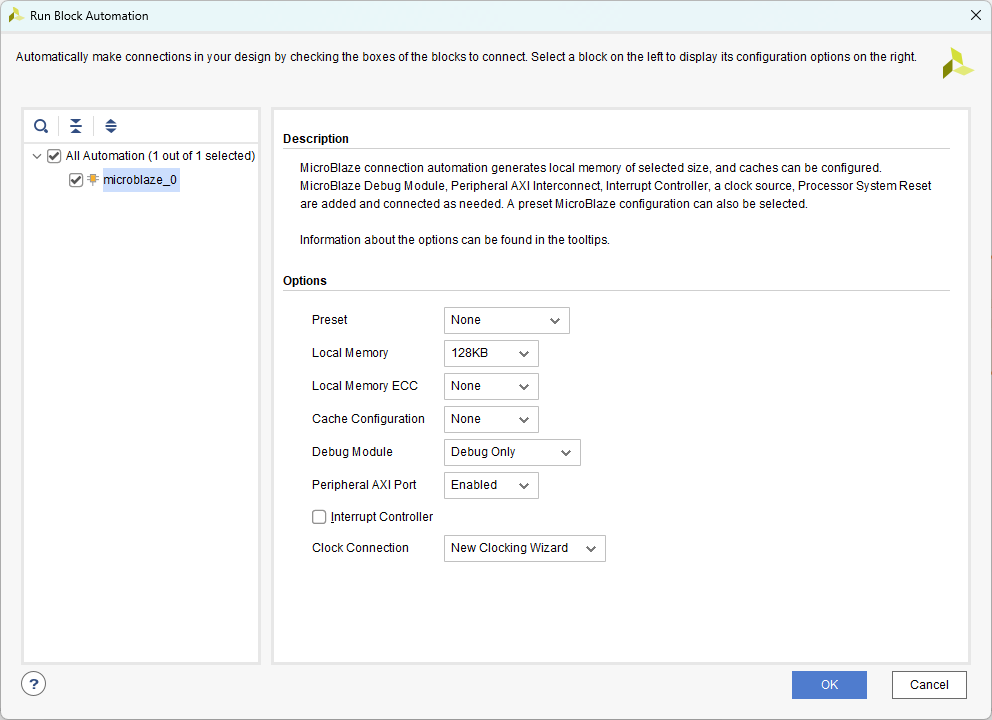

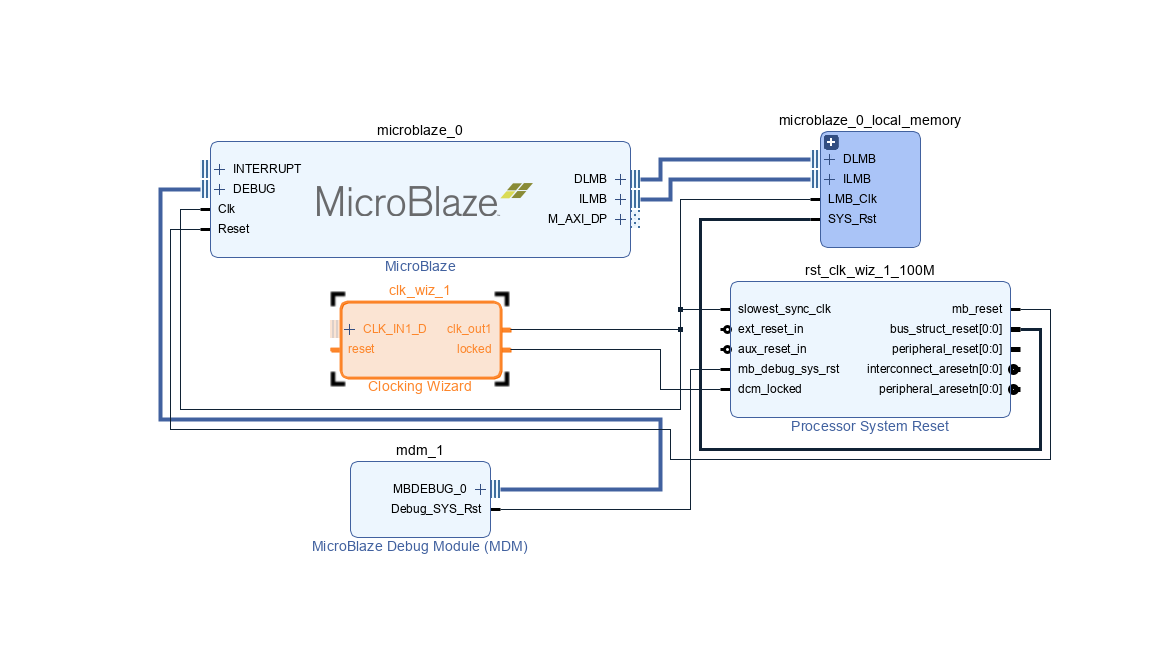

Run Block Automation 클릭

메모리 용량 넉넉하게 128KB 선택

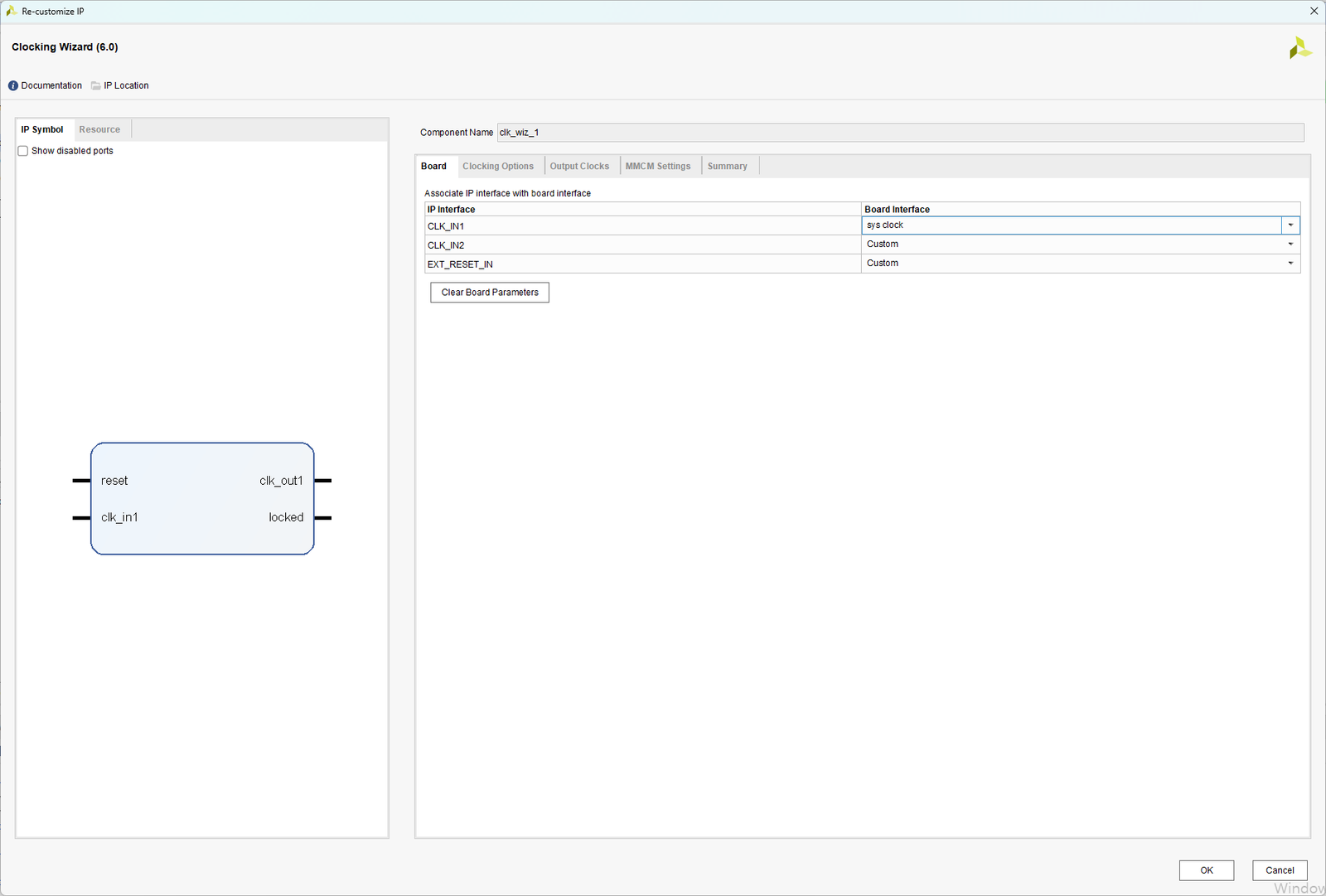

클락 설정 변경

살구색으로 표시된 clk_wiz_1 더블 클릭

CLK_IN1을 sys clock으로 변경 후 OK

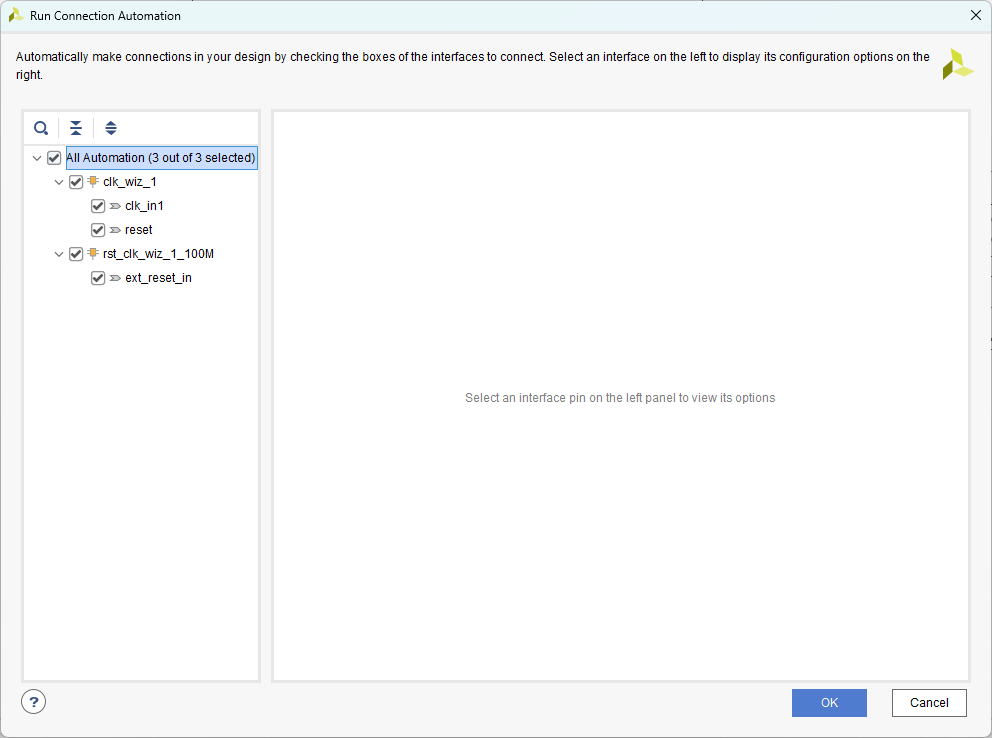

Run Connection Automation 클릭

모두 선택 후 OK

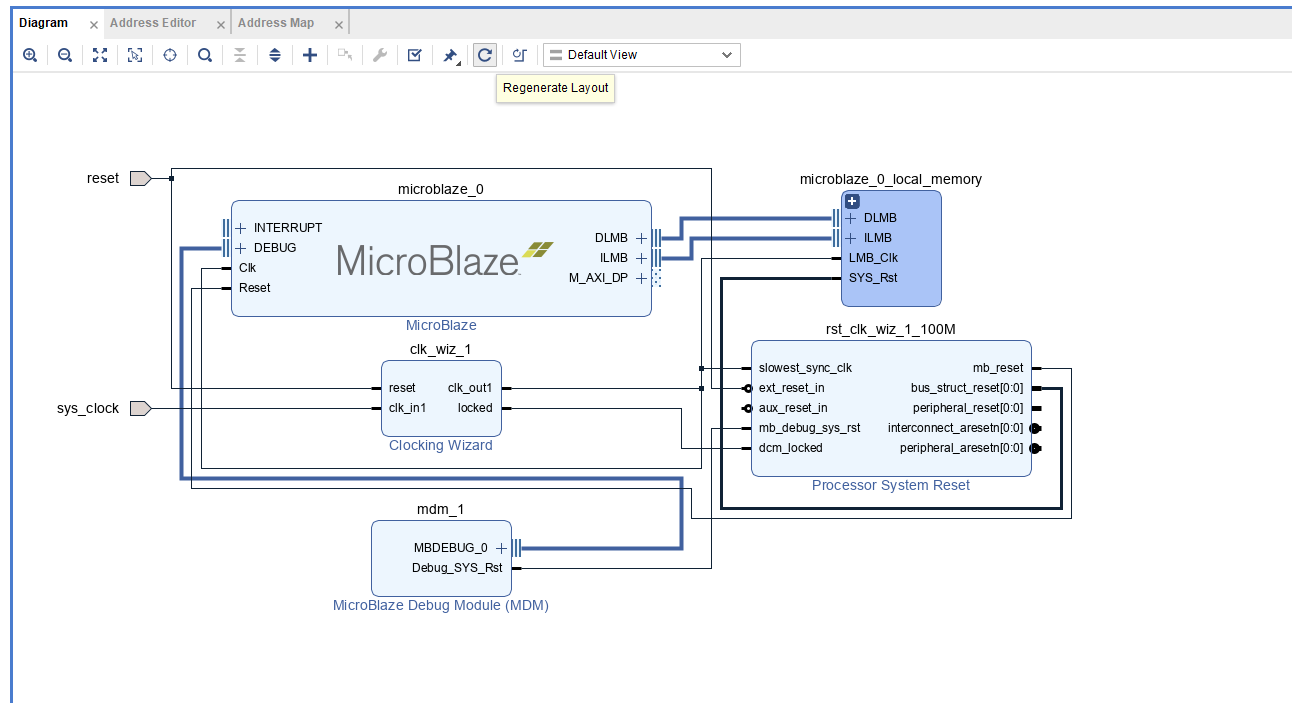

Regenerate Layout 클릭하여 재정렬

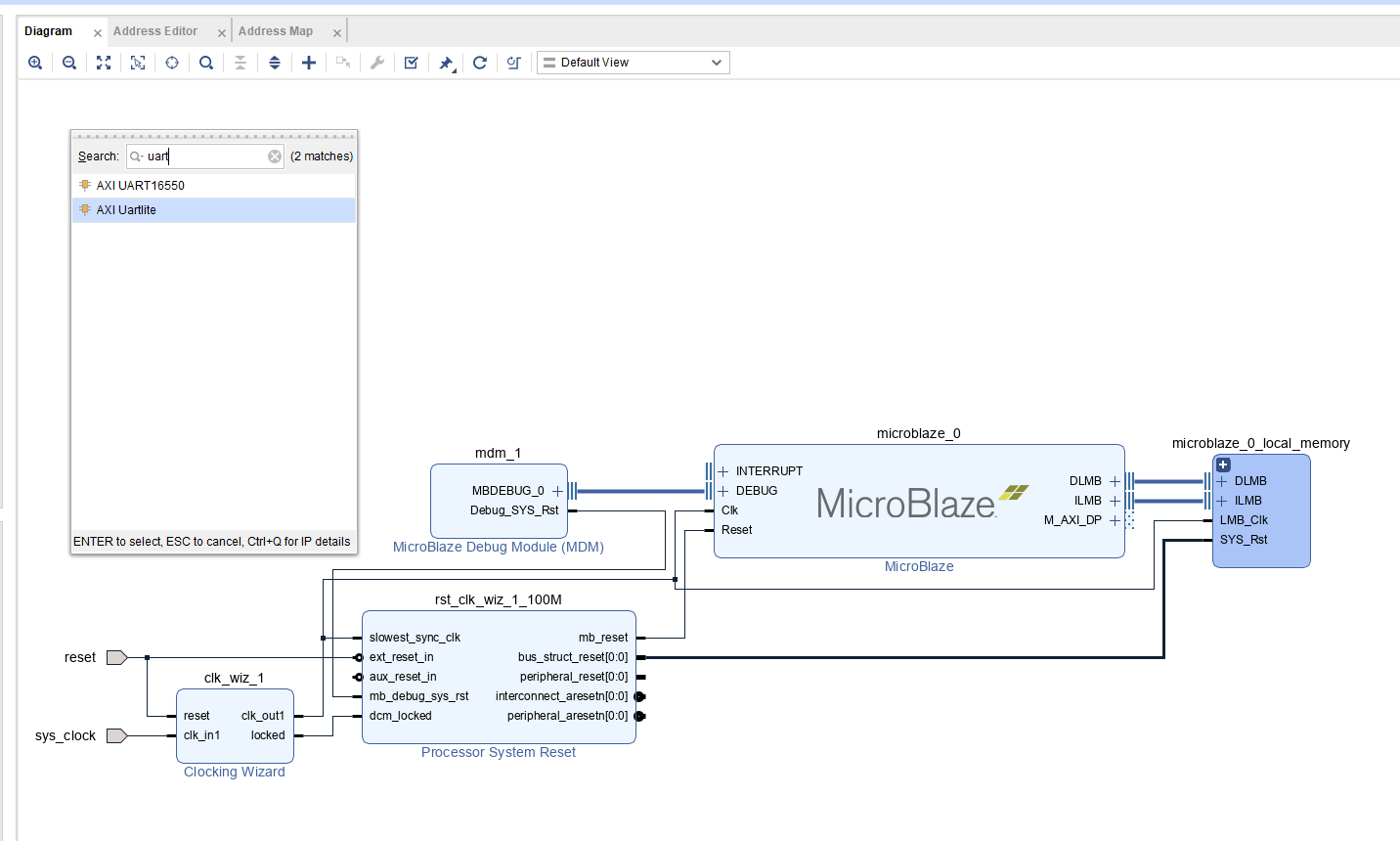

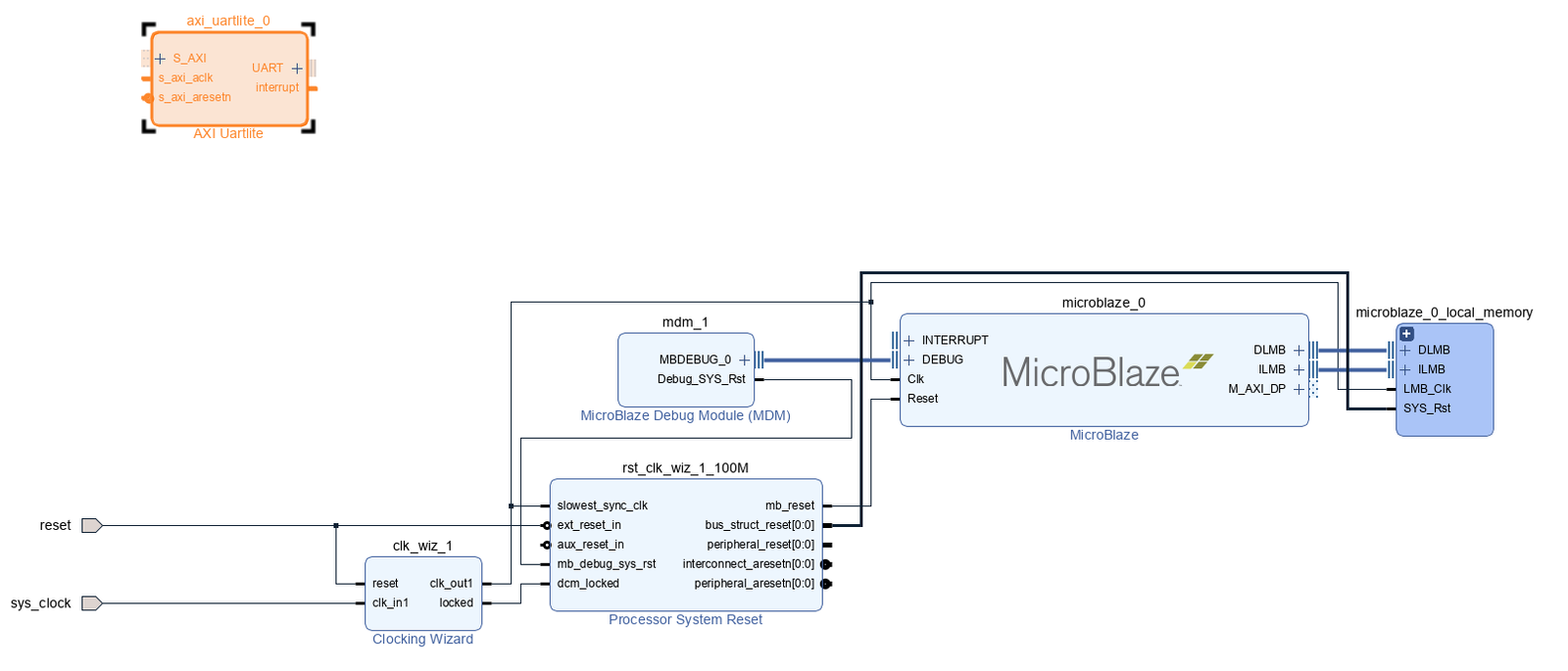

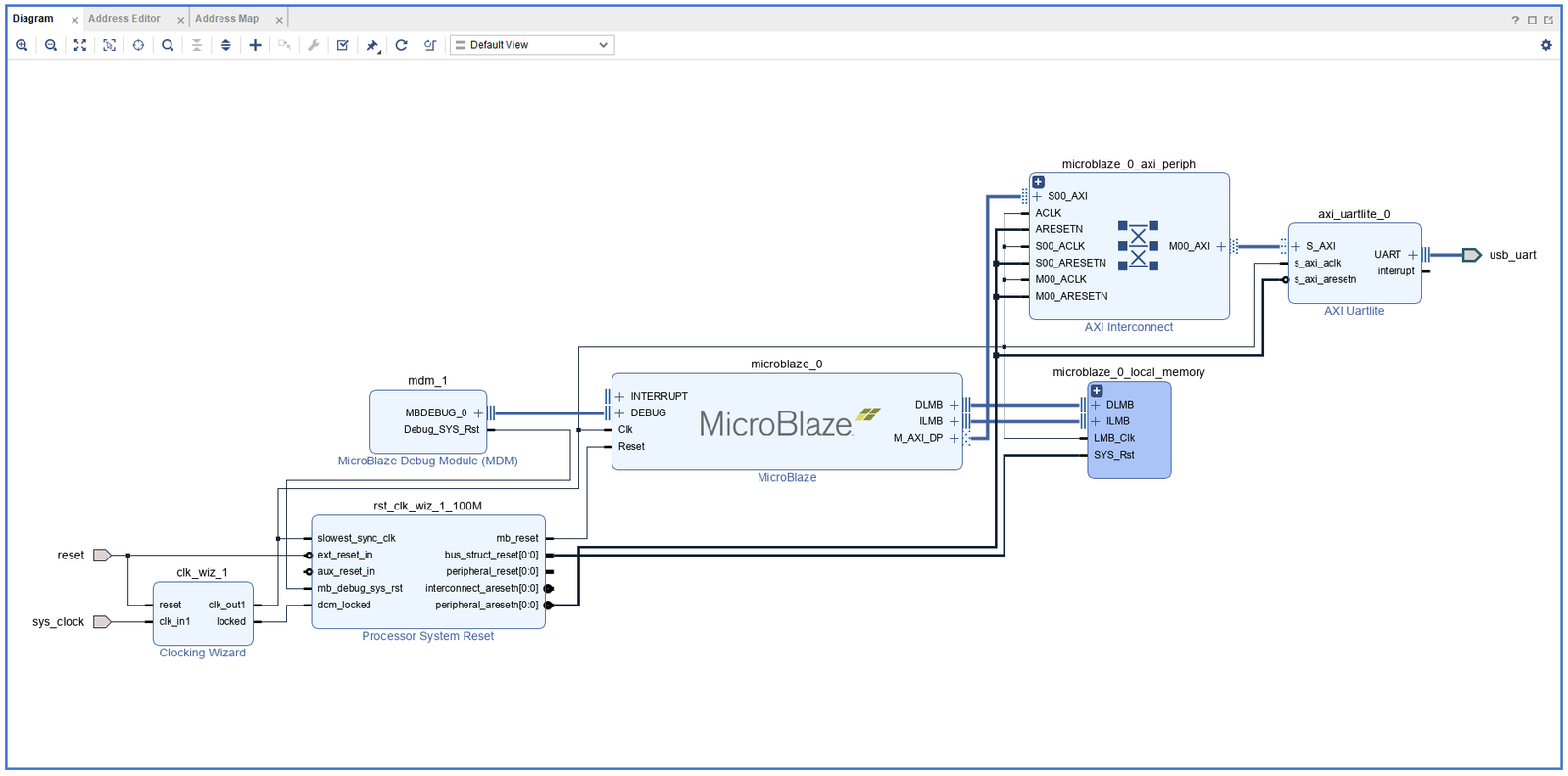

uart 추가

Uart 모듈은 기본적으로 추가해주는 게 좋다.

2개 뜨는 것 중 AXI Uartlite 선택

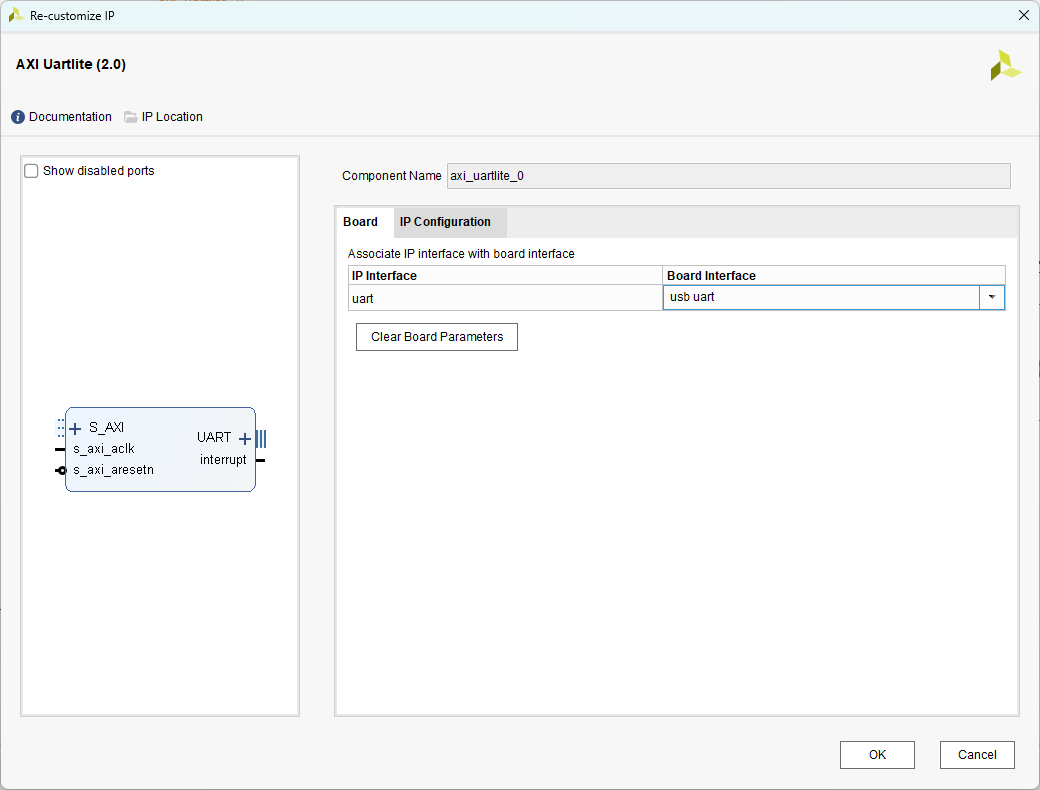

UART 모듈 더블 클릭

usb uart로 변경

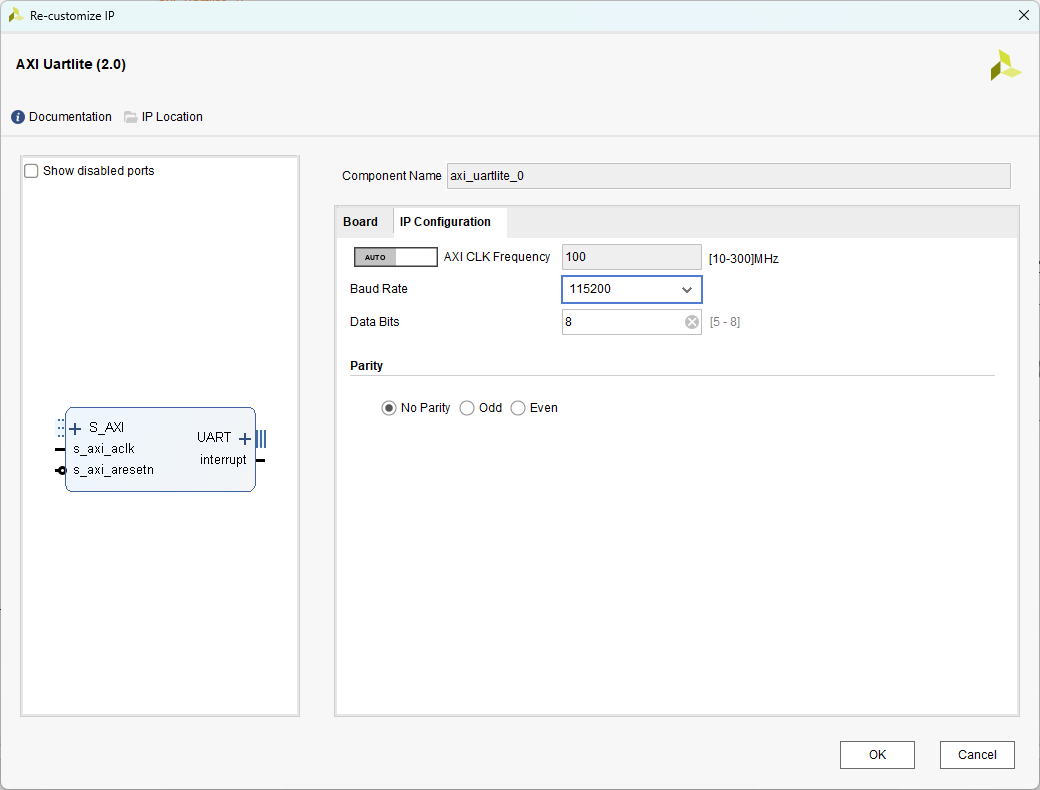

사용하고 싶은 Baud Rate 설정 후 OK

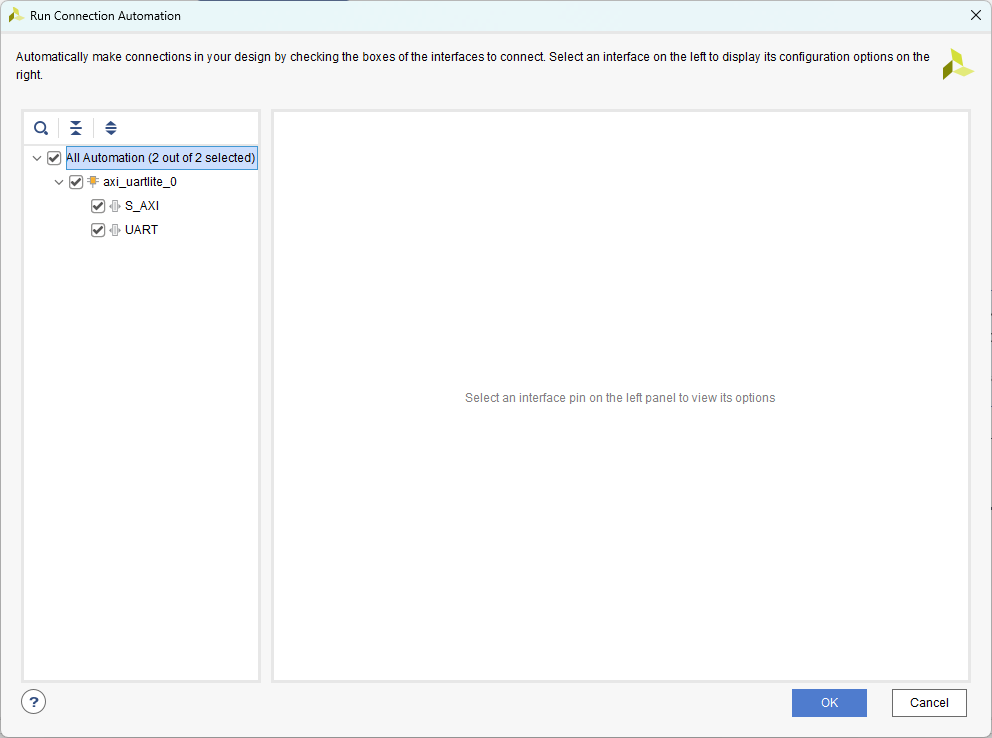

Run Connection Automation 클릭

모두 선택 후 OK

GPIO IP 추가

이전 포스팅에서 만든 GPIO IP를 추가해보자.

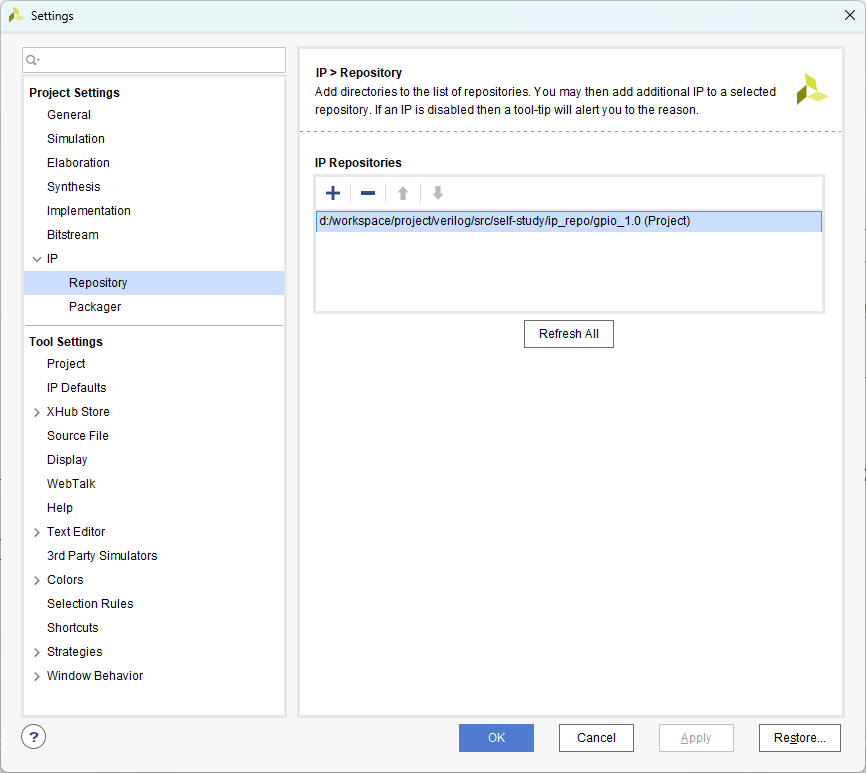

설정 확인

Settings 클릭

IP Repository에 이전에 만든 IP의 경로가 있는지 확인.

없으면 +버튼을 눌러서 추가 후 OK

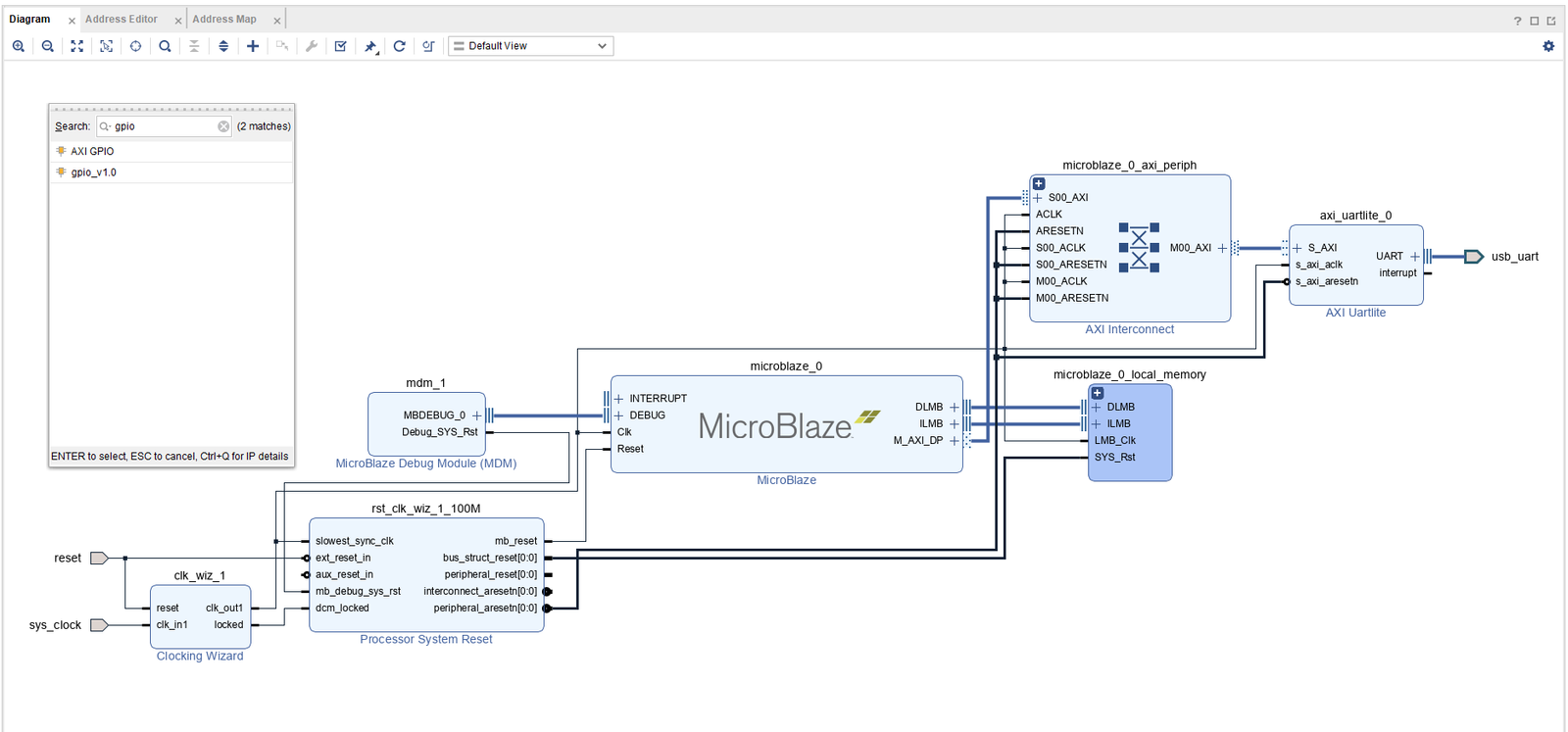

+버튼을 누르고 gpio 검색 후 내가 만든 IP를 선택(여기서는 gpio_v1.0)

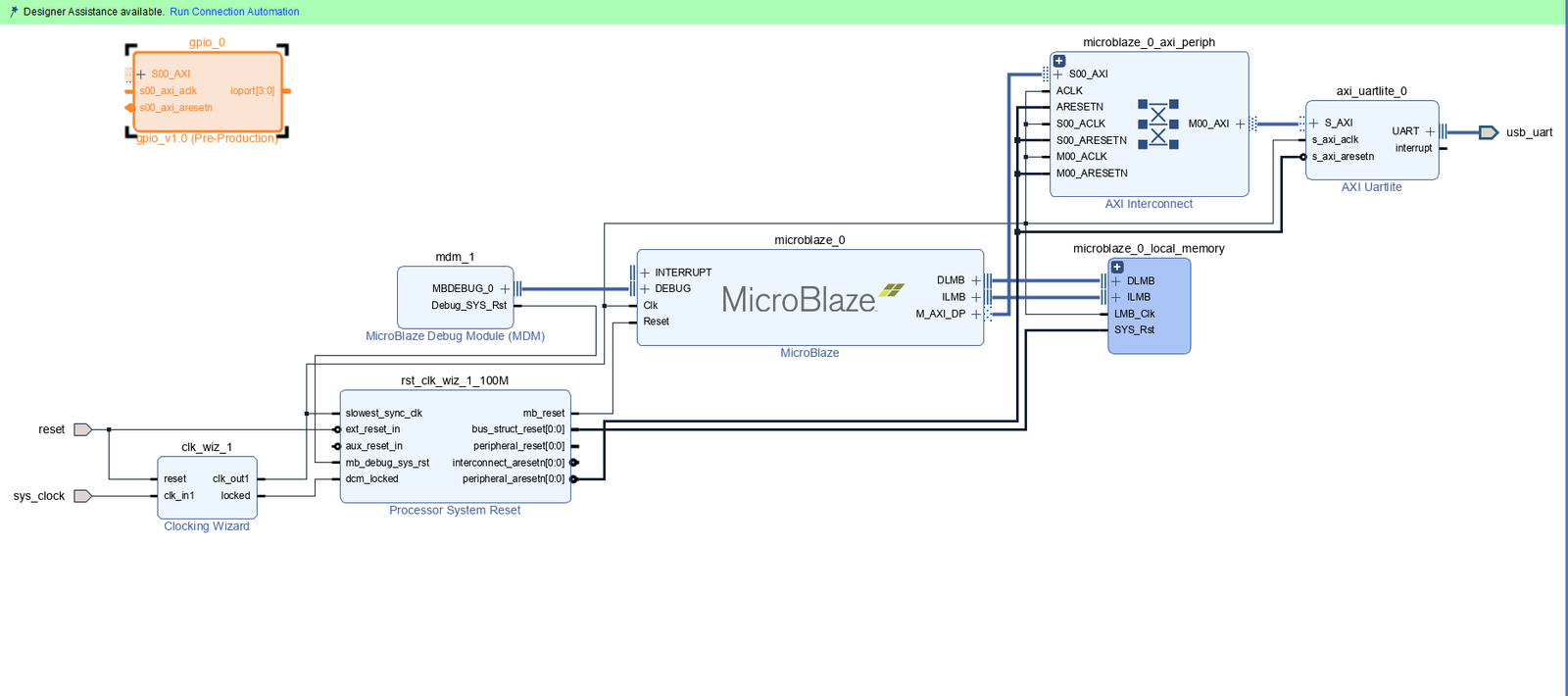

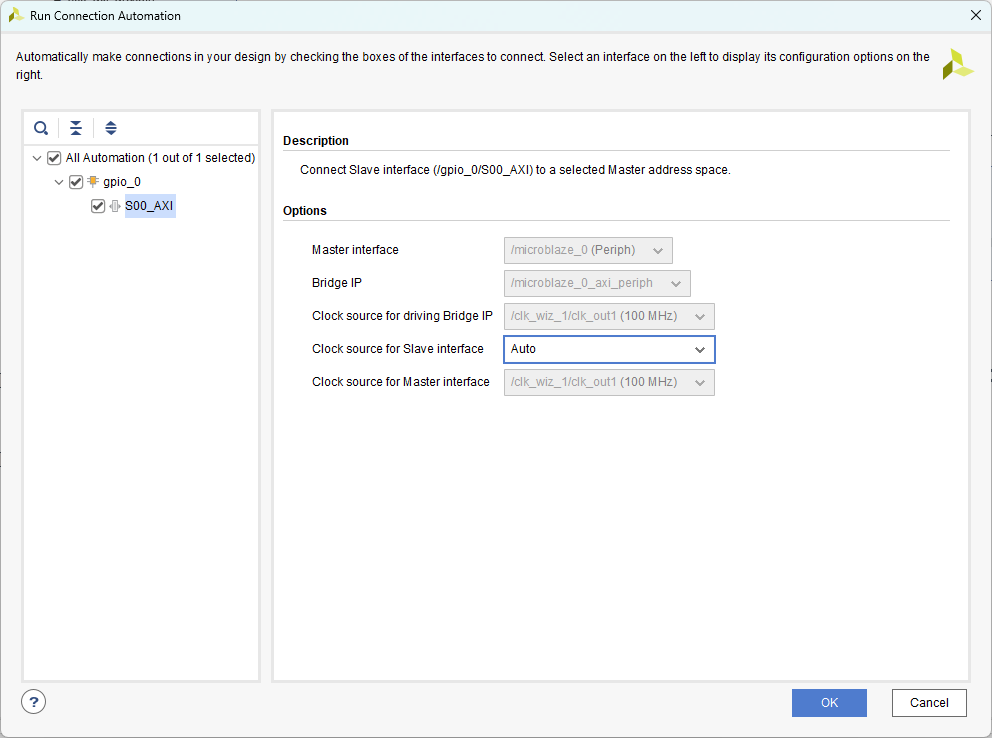

Run Connection Automation 클릭

모두 선택 후 OK

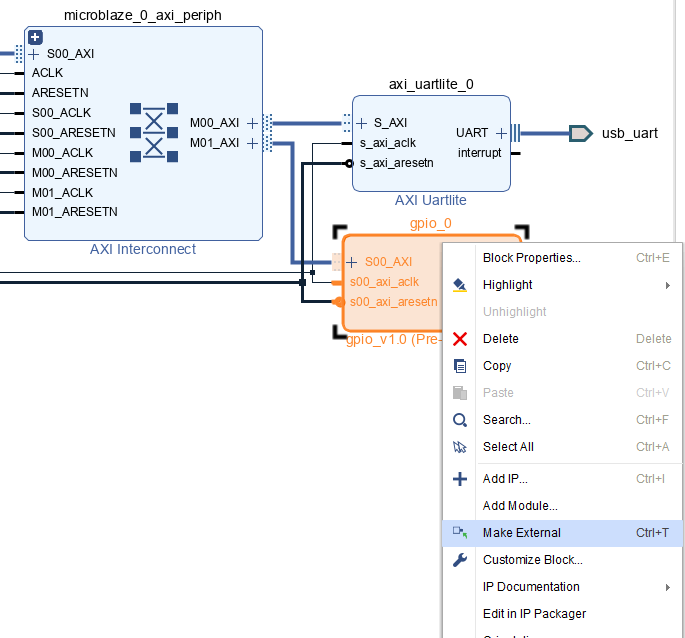

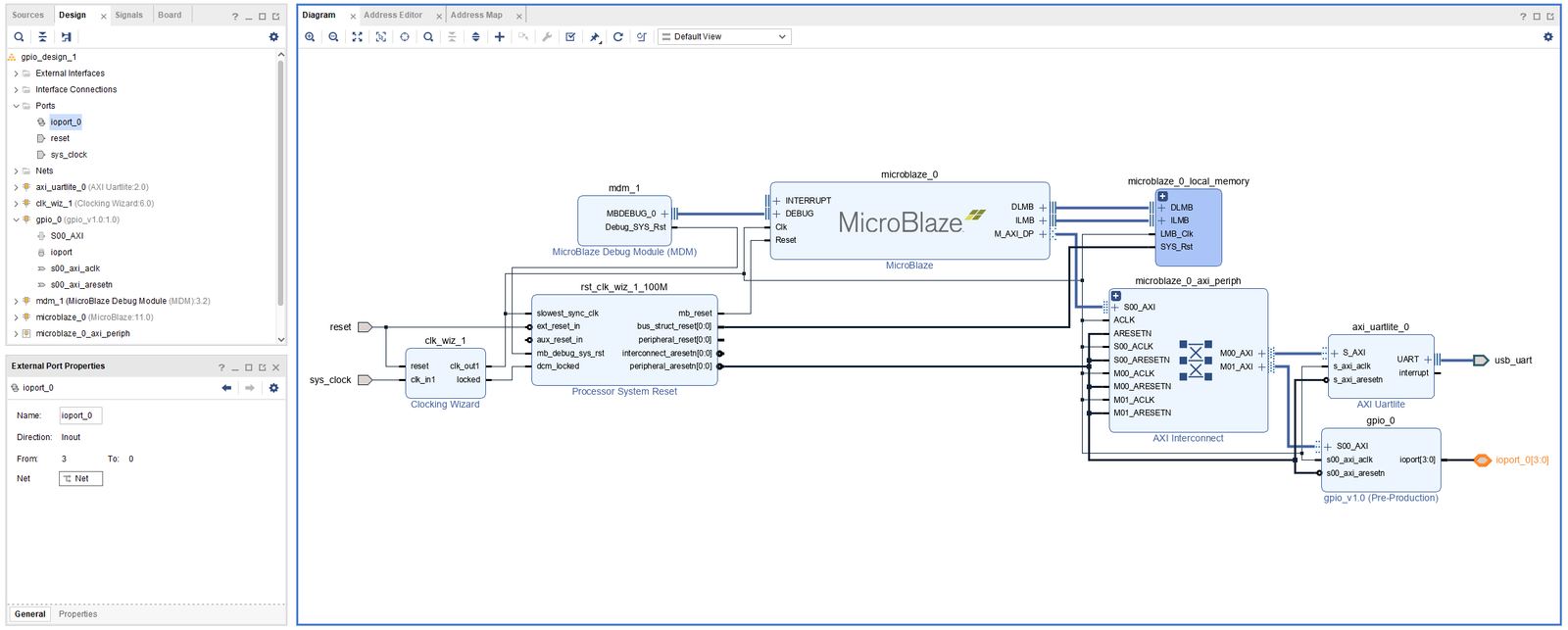

자동 연결은 됐으나 ioport쪽 포트가 달리지 않았으므로 모듈 우클릭 후 Make external 클릭

포트 이름을 바꿔주기 위해 선택 후 좌측에 Properties에서 Name을 바꿔주면 된다.

GPIO 하나 더 추가

각 포트를 led와 btn으로 변경해줌

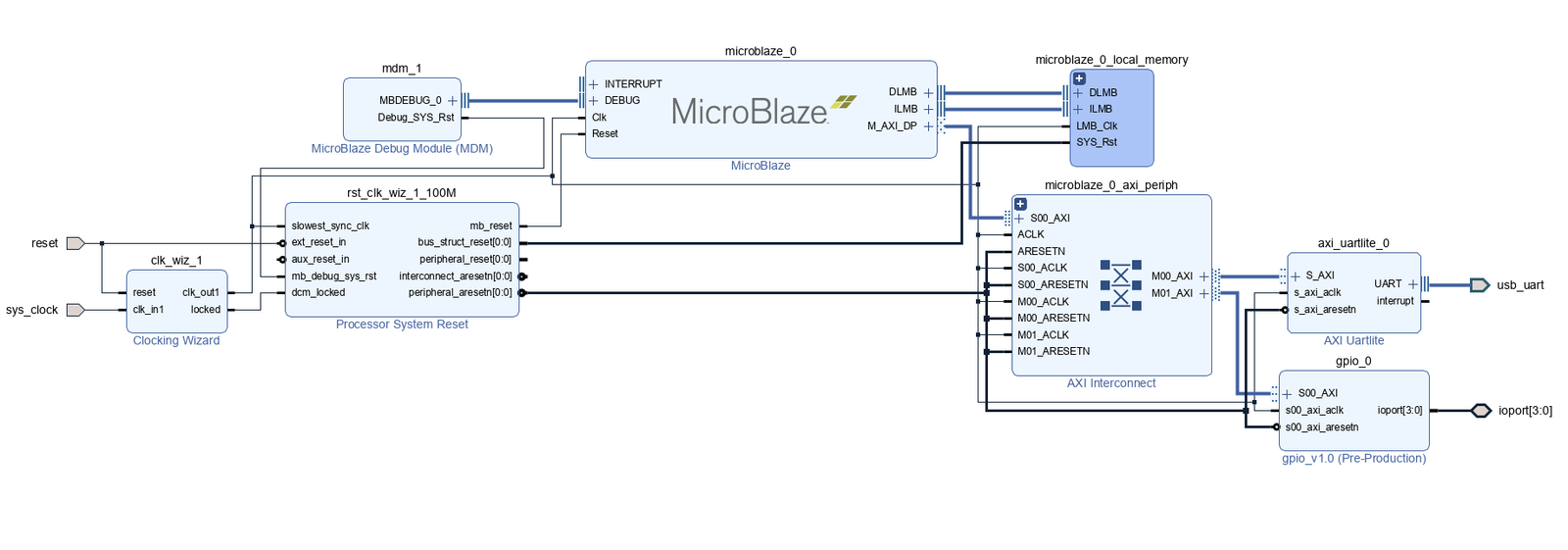

이렇게 블록 디자인이 완성되었다.

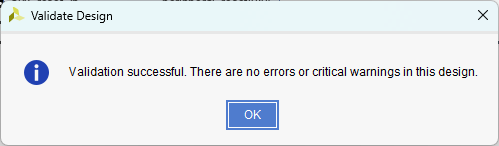

Validate

Validate Design 클릭

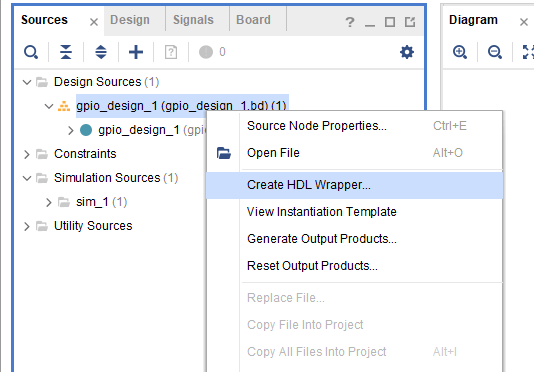

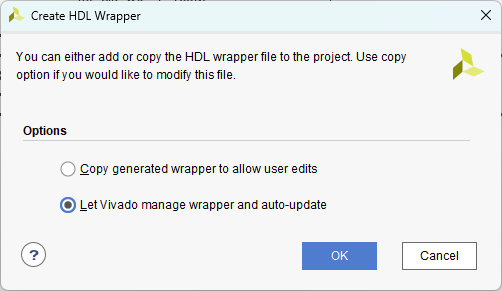

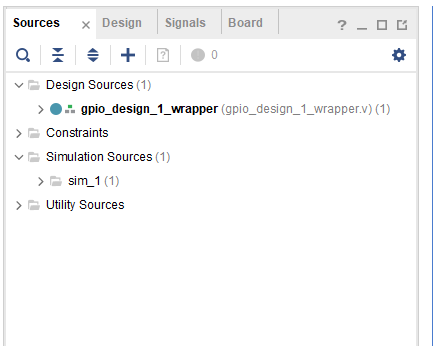

Wrapping 설정(한번만 해주면 추후 수정 시 자동 래핑됨)

블록 디자인(.bd 파일)은 Vivado 내부 포맷이기 때문에 이 자체로는 합성이 되지 않음

그래서 블록 디자인의 입출력 포트를 그대로 가진 Verilog 모듈로 감싸는 것이 Wrapping 작업임.

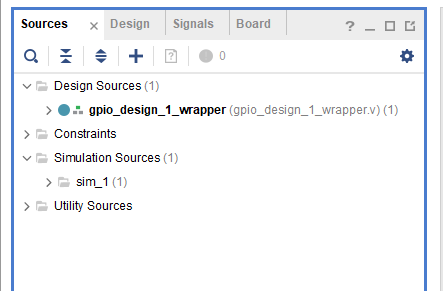

왼쪽에 주황색으로 표시된 곳을 우클릭하여 Create HDL Wrapper 클릭

OK

색상이 파란색으로 된 것을 확인할 수 있음.

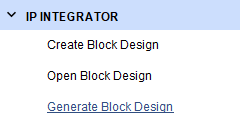

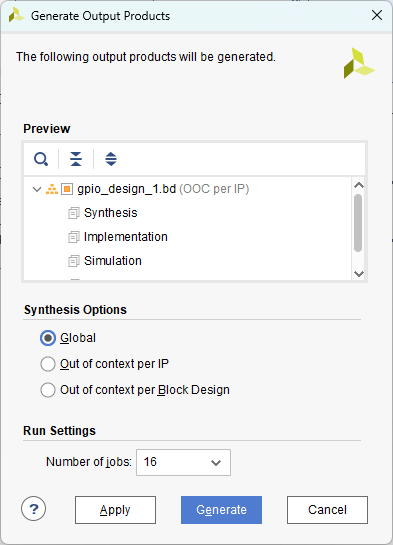

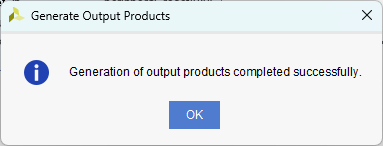

Generate Block Design(블록 디자인 수정 시마다 해줘야 함)

Generate Block Design 클릭

Global로 설정 후 Generate 클릭

Bitstream 생성 및 XSA Export

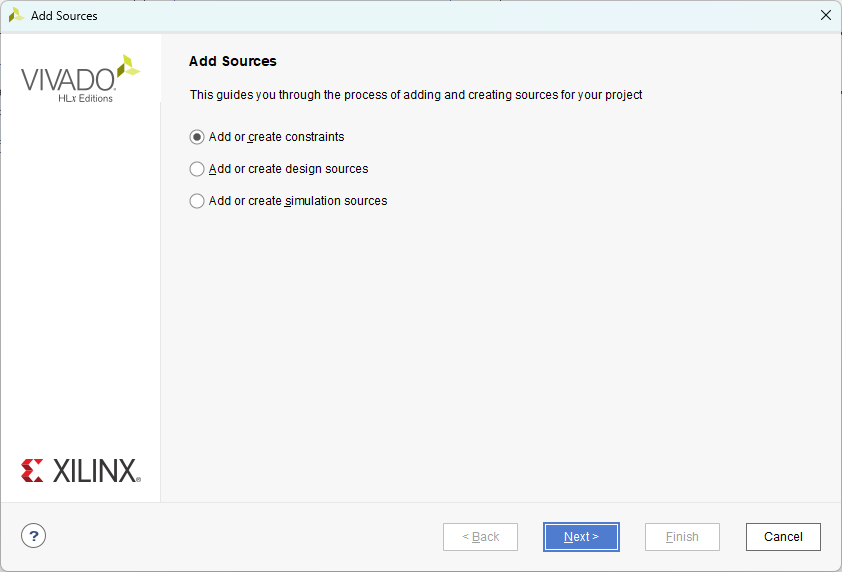

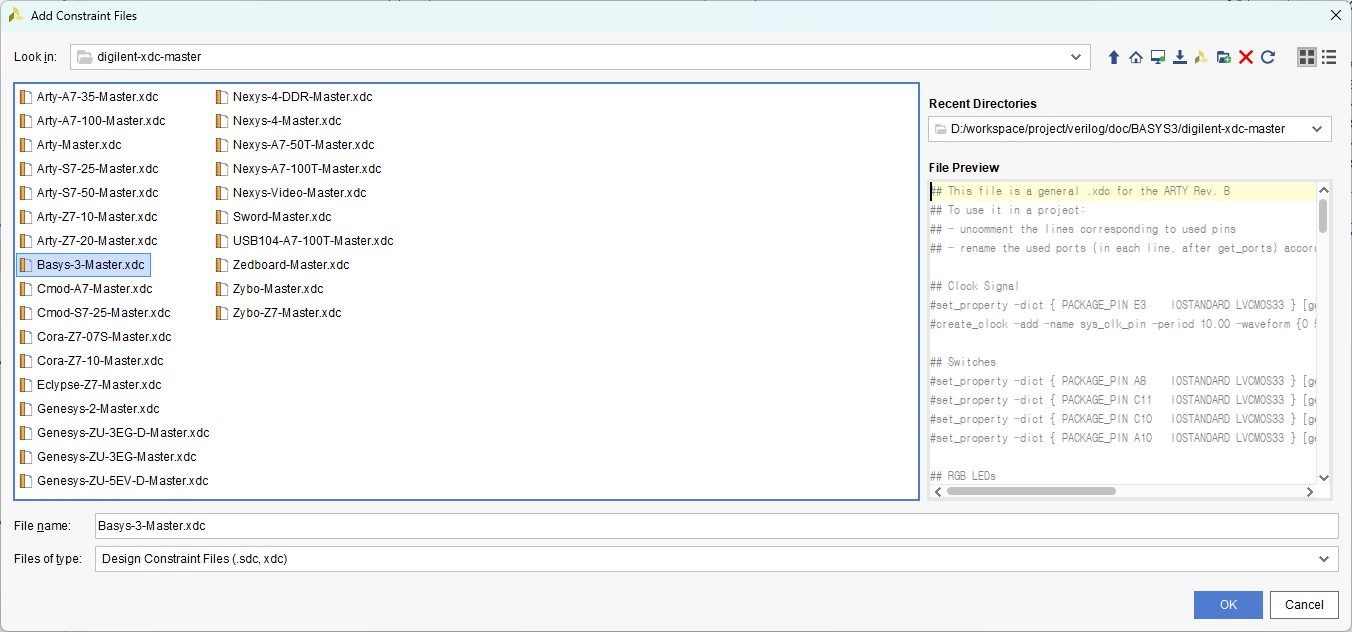

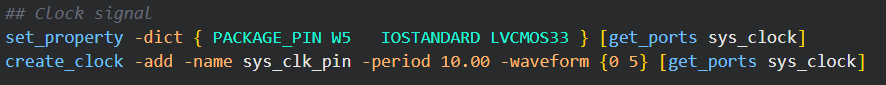

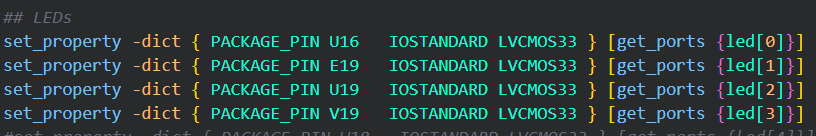

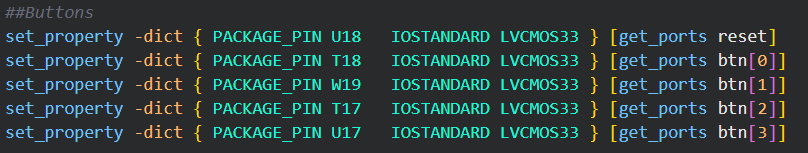

XDC 파일 설정

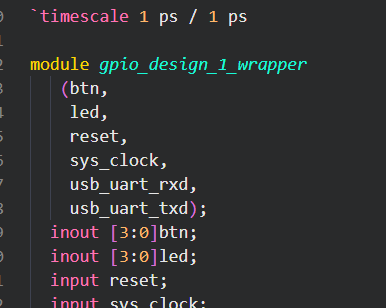

Wrapping에서 생성됐던 파일을 열어보기

여기에서 선언된 포트와 같이 XDC 파일을 변경하되, uart는 XDC에 추가해줄 필요 없음

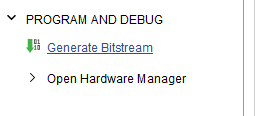

Bitstream 생성

OK 눌러서 비트스트림 생성

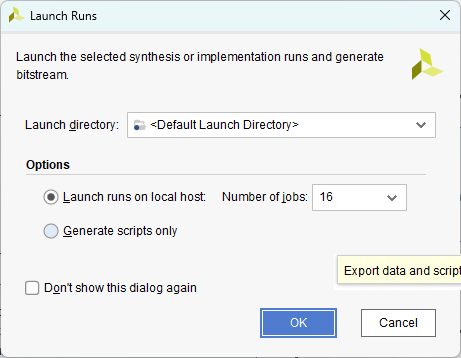

완료됐으면 Cancel 클릭

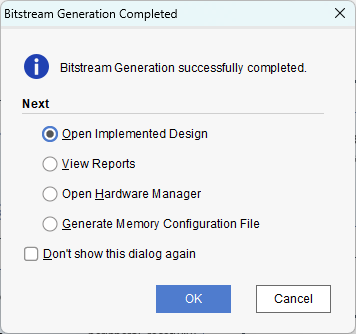

XSA Export

File – Export – Export Hardware 클릭

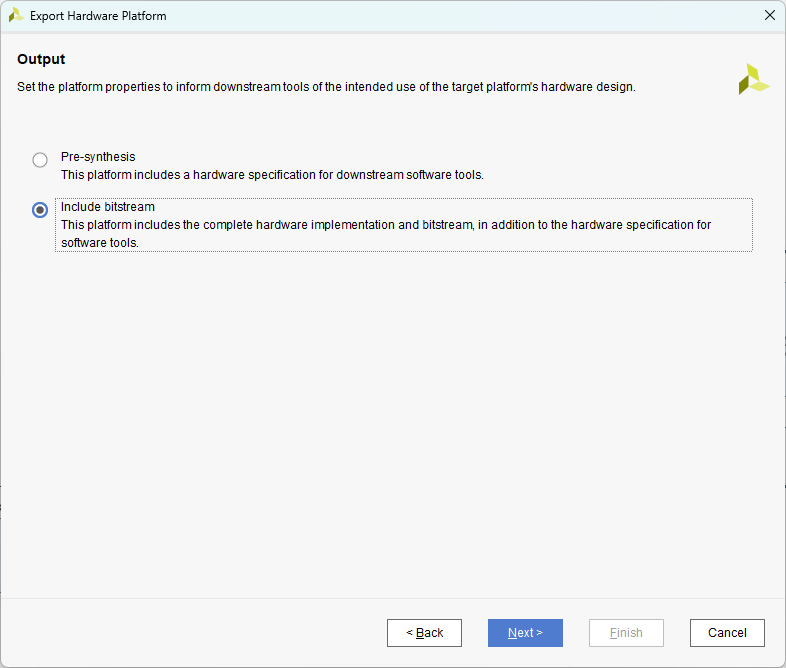

Include bitstream 클릭 후 Next

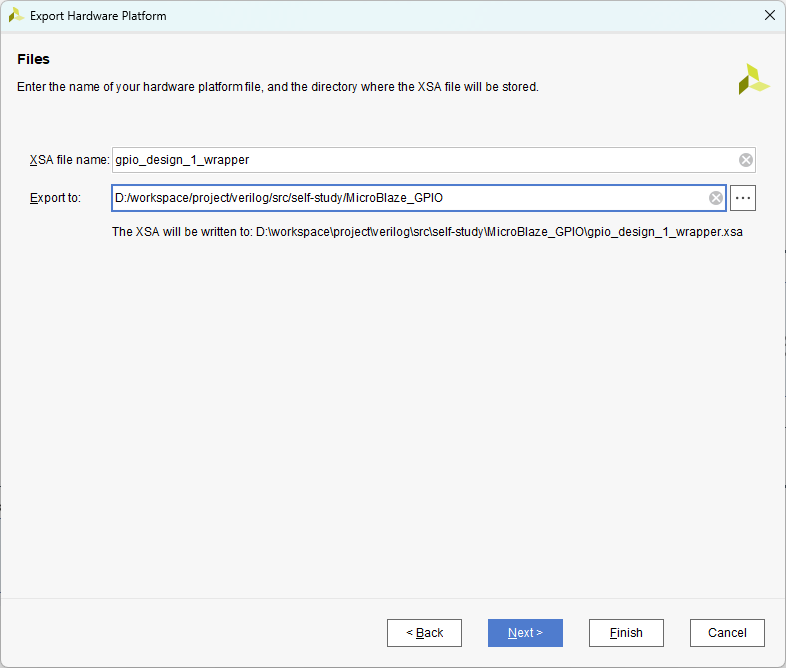

Next 클릭

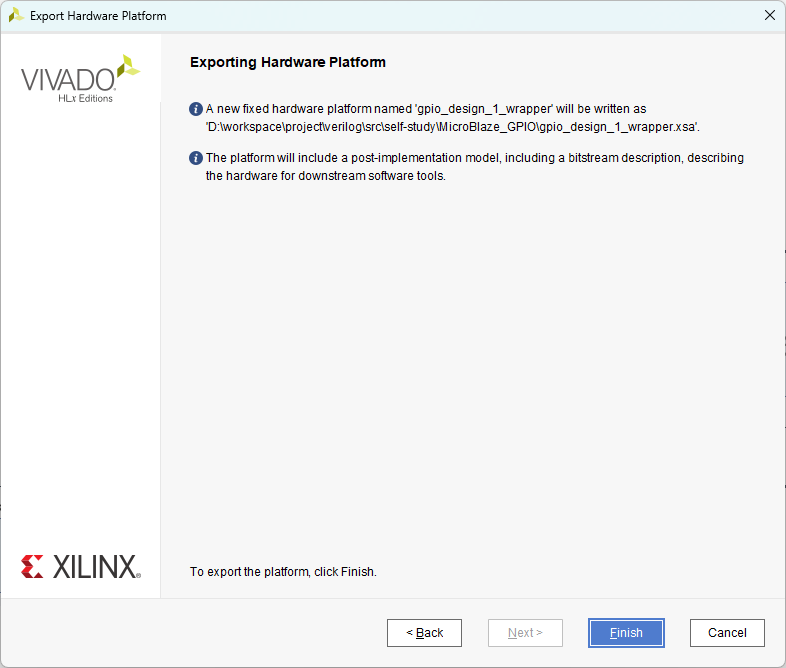

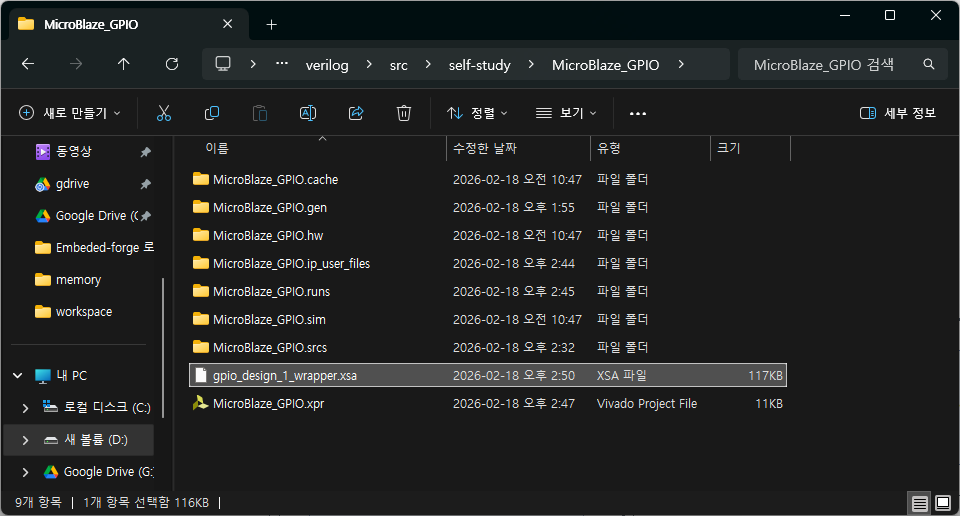

Finish 클릭하면 다음과 같이 xsa 파일이 생성됨

Vitis IDE 실행

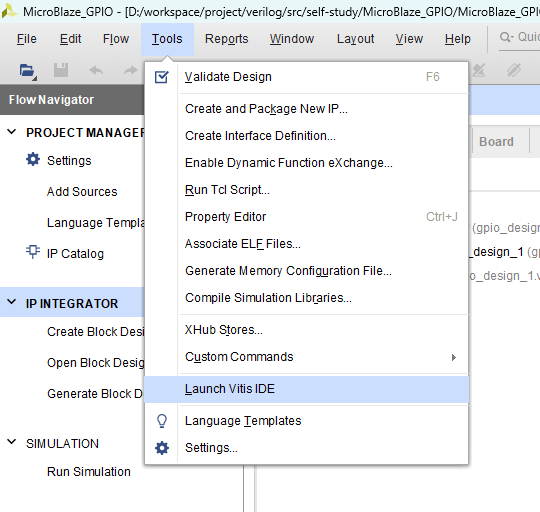

Tools – Launch Vitis IDE 클릭

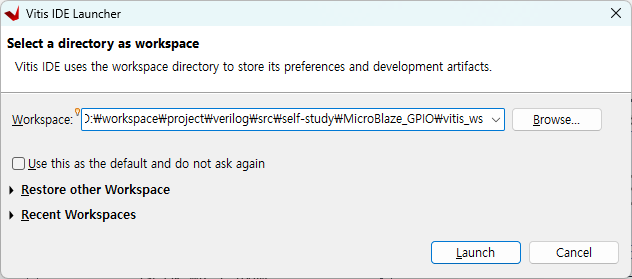

프로젝트 안에 vitis_ws라는 폴더를 만들어주었고 그곳을 워크스페이스로 경로 설정해주었다.

Launch 클릭

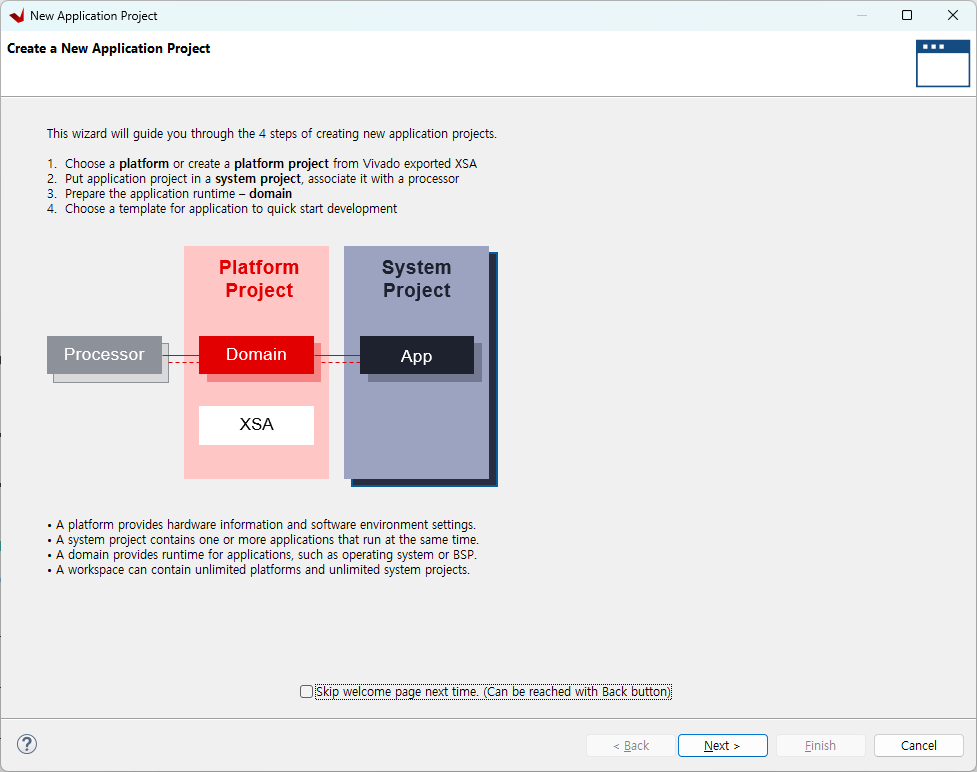

프로젝트 생성

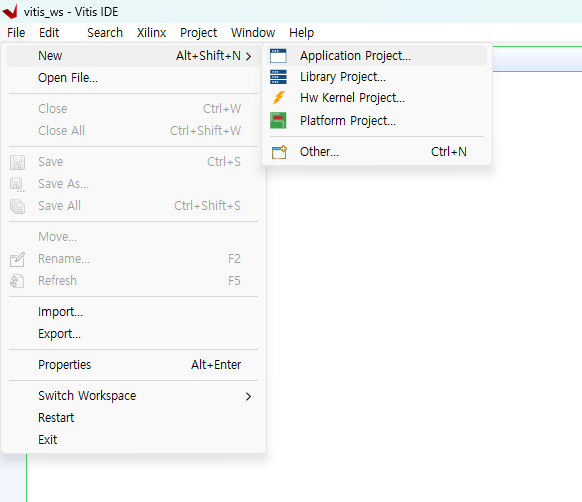

File – New – Application Project 클릭

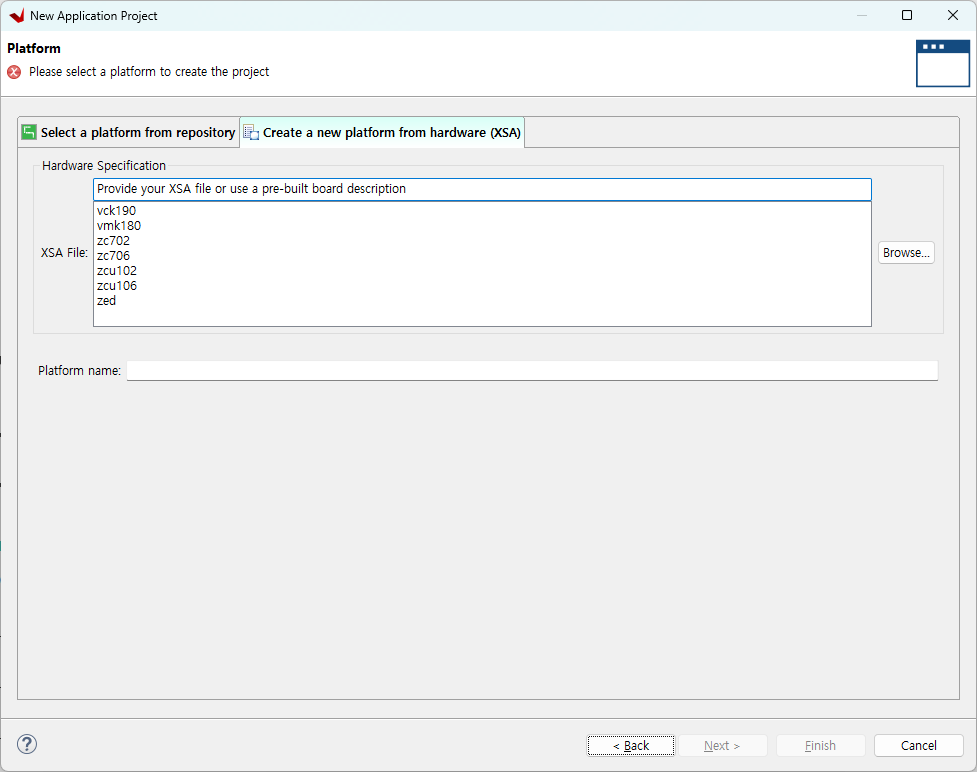

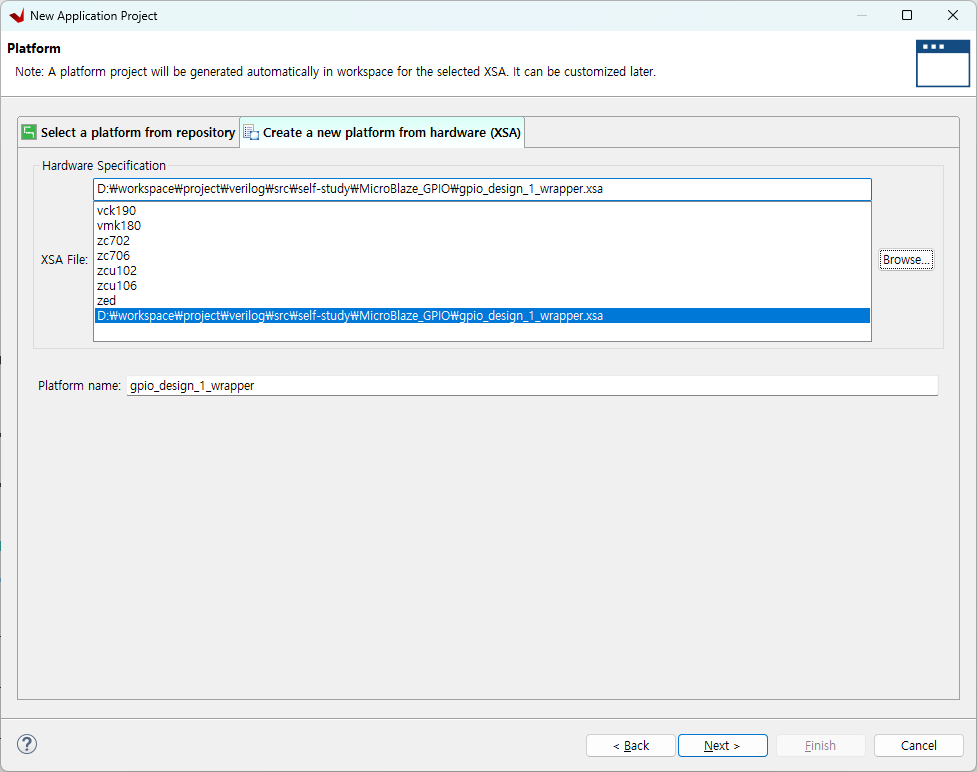

Browse 클릭하여 아까만든 XSA 파일 경로를 넣어줌

Next 클릭

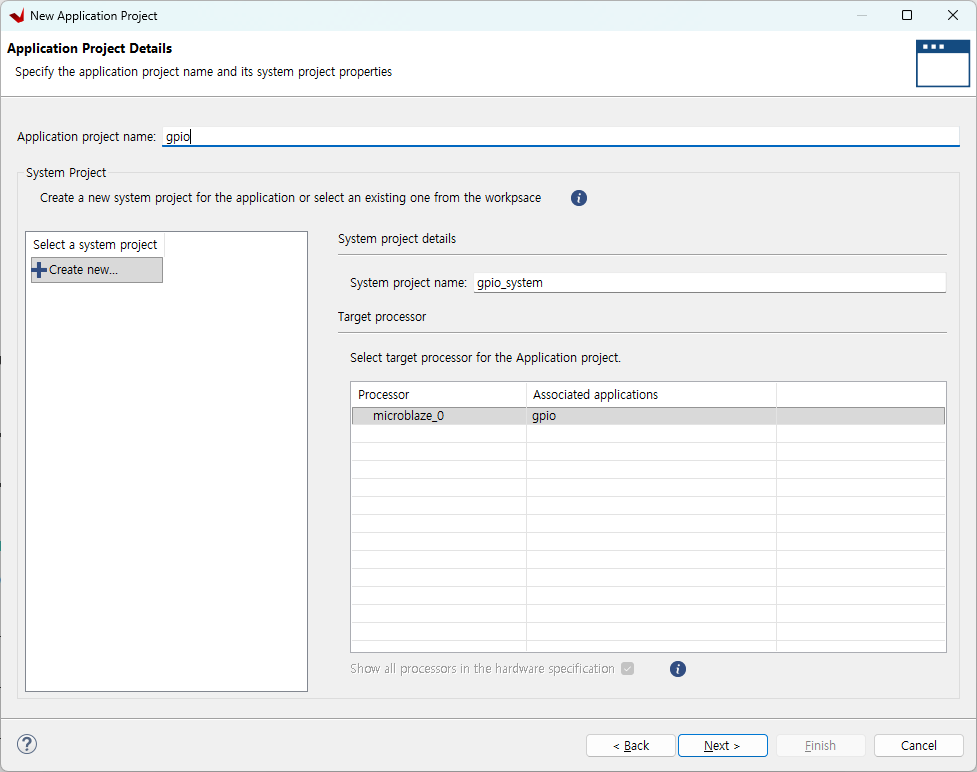

프로젝트 이름을 적어줌

Next 클릭

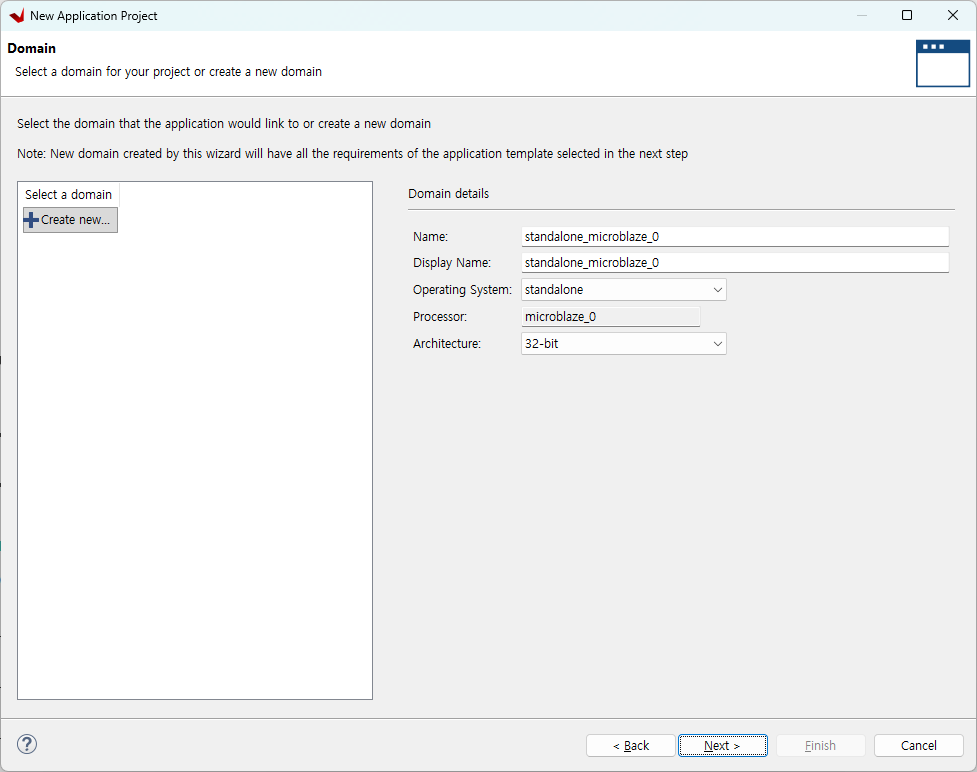

Next 클릭

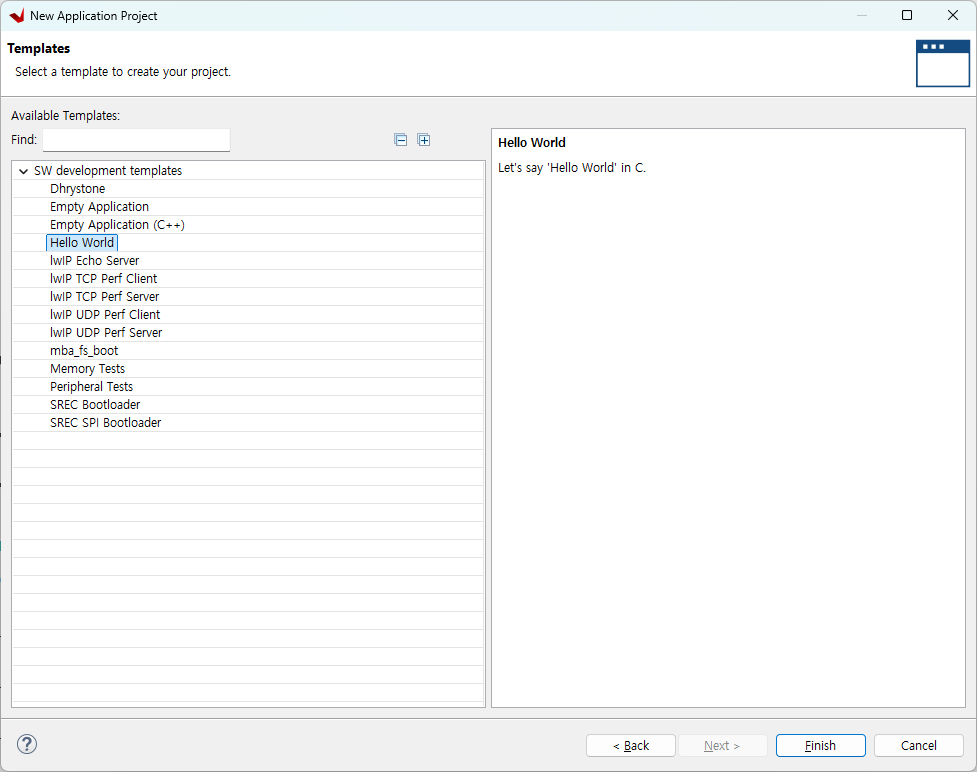

여기에서 Empty Application을 선택할 수도 있고 Hello World를 선택할 수도 있는데

여기서는 Uart를 활용하기 위해 Hello World로 하였다.

Hello World 선택 후 Finish

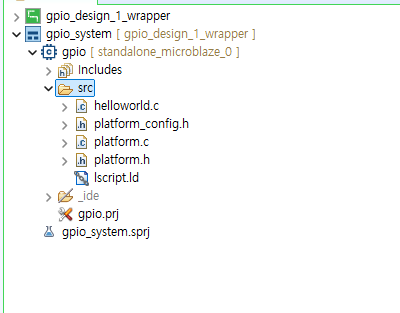

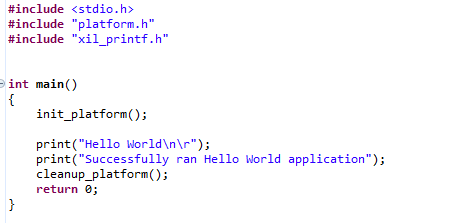

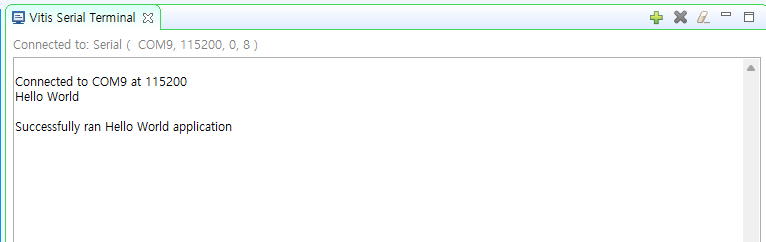

소스 코드가 이렇게 작성되어 있으므로 빌드해서 실행해보면 실행이 되는데

시리얼모니터를 띄우고 리셋버튼을 누르면 다음과 같이 뜨는 것을 확인할 수 있음

어쨌든 여기에서 코드를 시작하도록 하자.

우선 helloworld.c는 나중에 필요 시 참고만 하고 동작을 안하게 하기 위해 모두 주석처리해주었다.

GPIO 코드 수정

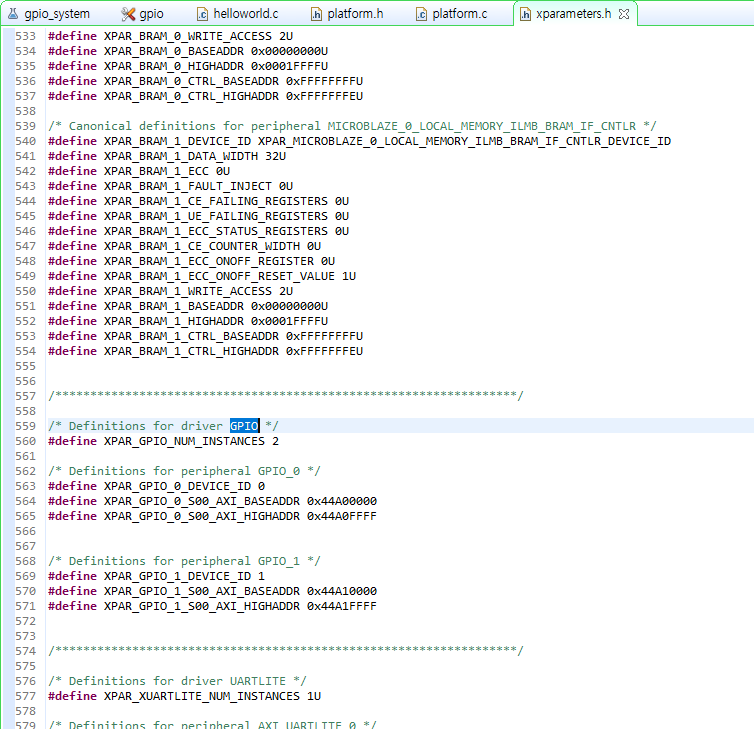

일단 xparameters.h 파일에 들어가면 다음과 같이 GPIO가 메모리맵에 있는 것을 확인할 수 있다.

/* Definitions for driver GPIO */

#define XPAR_GPIO_NUM_INSTANCES 2

/* Definitions for peripheral GPIO_0 */

#define XPAR_GPIO_0_DEVICE_ID 0

#define XPAR_GPIO_0_S00_AXI_BASEADDR 0x44A00000

#define XPAR_GPIO_0_S00_AXI_HIGHADDR 0x44A0FFFF

/* Definitions for peripheral GPIO_1 */

#define XPAR_GPIO_1_DEVICE_ID 1

#define XPAR_GPIO_1_S00_AXI_BASEADDR 0x44A10000

#define XPAR_GPIO_1_S00_AXI_HIGHADDR 0x44A1FFFF

- GPIO 인스턴스가 2개라고 잡힘

- 0번 디바이스의 메모리 맵 주소: 0x44A00000 ~ 0x44A0FFFF

- 1번 디바이스의 메모리 맵 주소: 0x44A10000 ~ 0x44A1FFFF

이렇게 잡히면 정상이라고 보면 된다.

결론

이번 포스팅에서는 MicroBlaze에서 작업하기 위해 필요한 모든 설정을 해주었고 코딩만 하면 되는 상태로 만들어주었다.

xparameters.h 파일에서 내가 추가한 GPIO IP의 주소가 메모리 주소로 올라오는 것을 확인하였다.

다음 포스팅에서 코딩을 이어나가도록 하자.